# Extreme Patterning Solutions

Luigi Capodieci, Ph.D. R&D Fellow, DFM Director

# Outline

- •Patterning in *perspective*:

- -Variability in Lithographic Processes

- -Manufacturing Costs and Trends

- •Patterning and Physical Design

- -The case for DFM (Design for Manufacturing)

- Advanced Patterning at 22nm and below Systematic approaches to *managed variability* Source Mask/Design Optimization and "*pixelated*" OPC

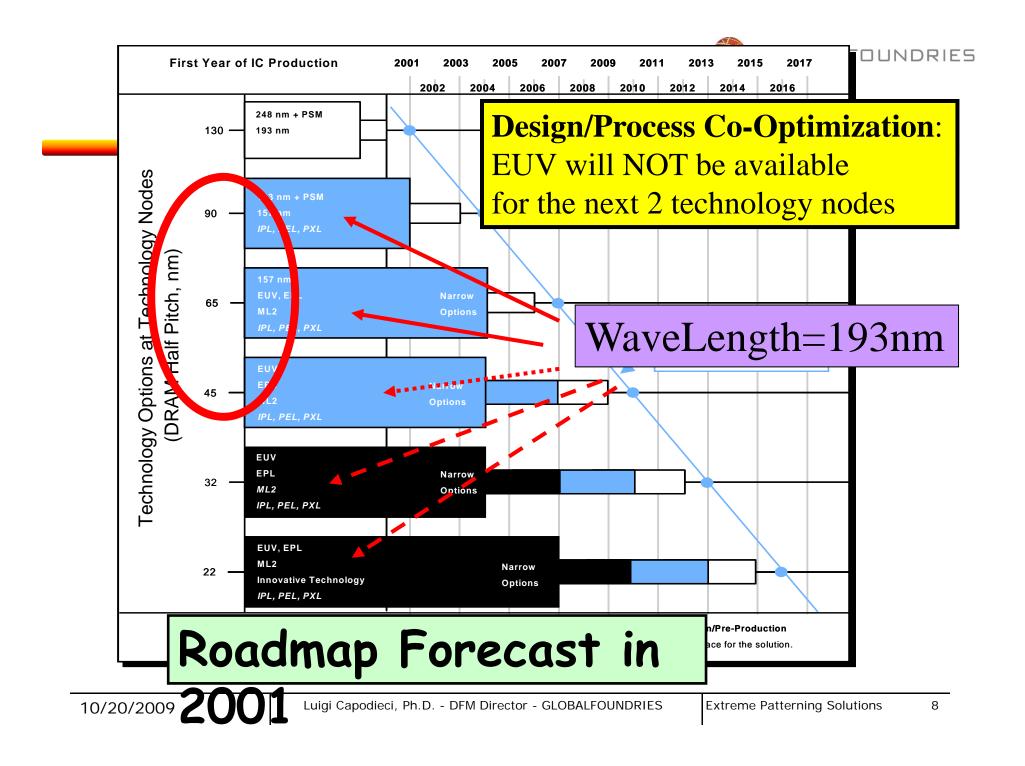

- •Extreme Patterning Solutions at 20nm and below:

- –Dual Mask (and Multi-Mask) Patterning Schemes

- -Novel Process Integration Schemes

- -EUV: good progress, but timing risk

- Analysis and Conclusion: "State" of Patterning

# Variability: key to patterning

- •At the limits of the "geometric scaling roadmap": variability as a percentage of feature size increases:

- -atoms don't scale

- -kt/q doesn't scale

- -photons don't scale

- •Main factors:

- -Intrinsic process variability

- -Environmental effects

- -Physical limits

- Variability affects Yield, Performance, and Power

- Variability can be classified as "random" and "systematic"

- –Physical limits cause "random" variations (e.g. dopant fluctuations)

10/20/2009

4

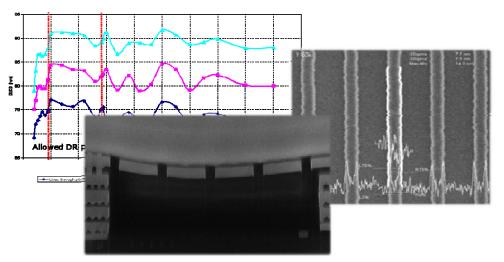

# Variability: length scale

- Variability occurs at different length scales

- -Across a single transistor (or wire)

- -Transistor to transistor

- -Across Die

- -Across Wafer

- -Wafer to Wafer

- -Lot to Lot

•Often systematic effects are considered random only because it is difficult (or impossible) to characterize them

5

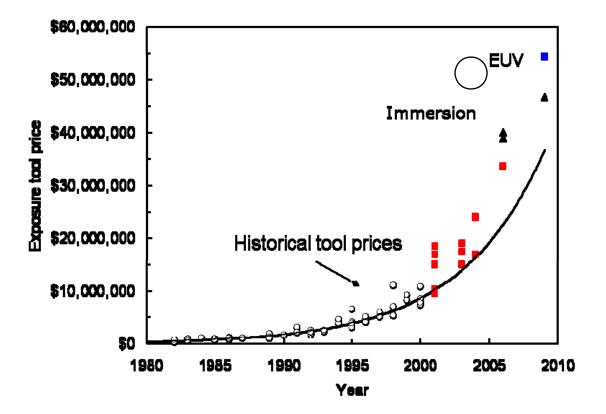

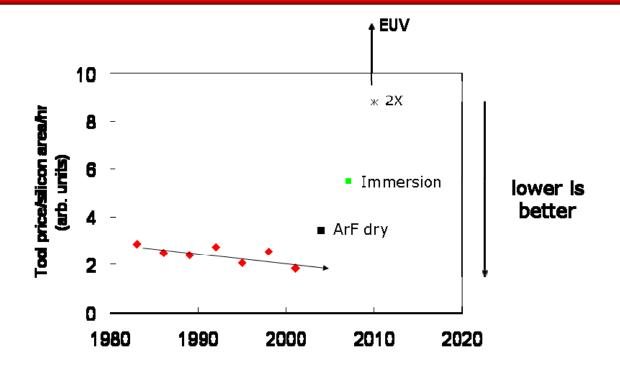

# Lithography Process Costs

- Costs of Single tool increasing by ~3x every 5 years

- Scanner for 45nm node costs \$40m

# Lithography Costs Per Unit Area

- -Wafer Size increases

- -Scanner Throughput (wafers per hour) increases

- -Net: cost per unit area declined down to 65nm node

- Increasing for 45 and 32nm nodes

- -Supports relatively constant cost per chip

7

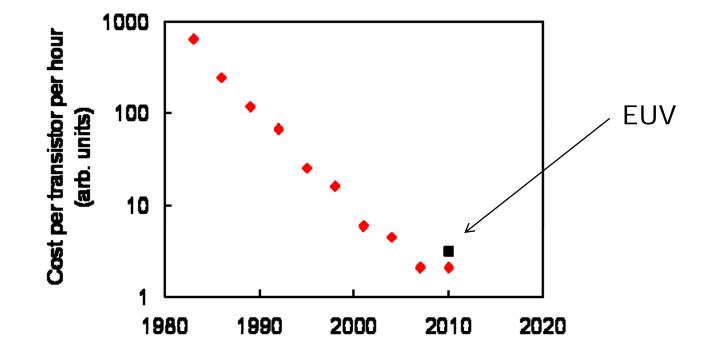

## Lithography costs – Per Transistor

Rapidly decreasing cost per transistor fuels semiconductor device and product innovation

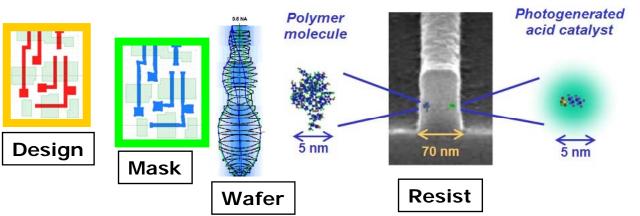

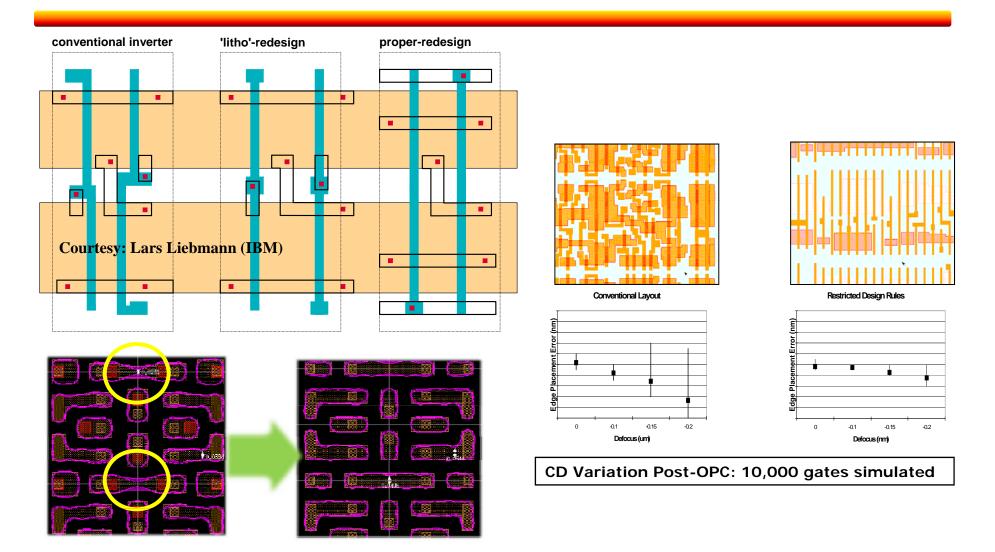

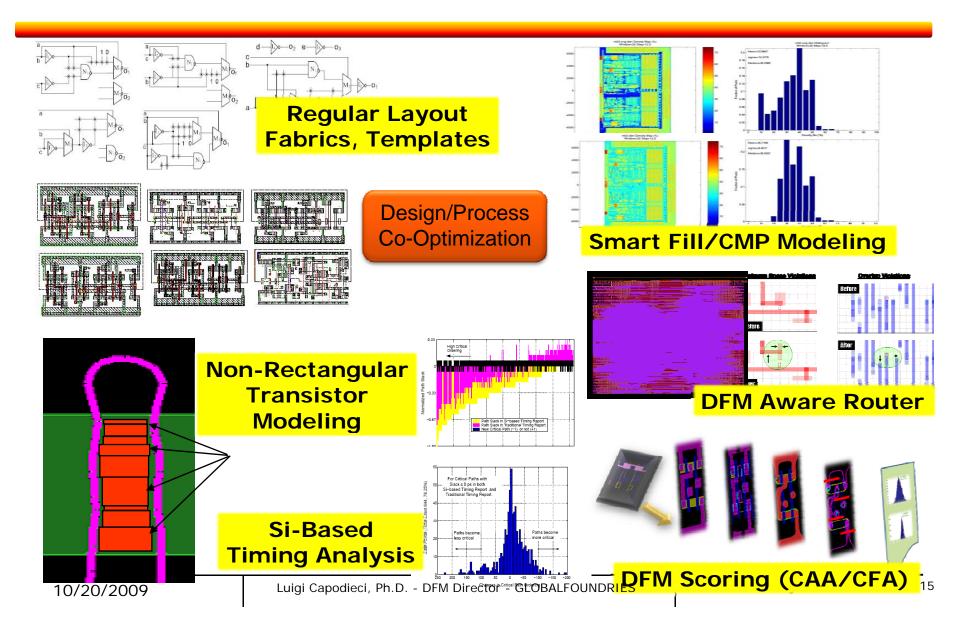

#### Patterning and Physical Design at 45nm

Courtesy of Kevin Lucas (Freescale, Synopsys)

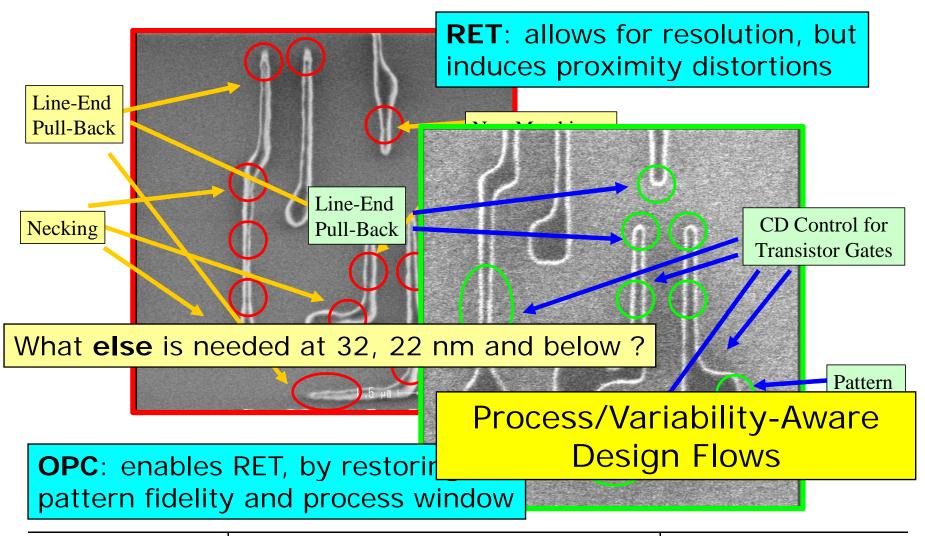

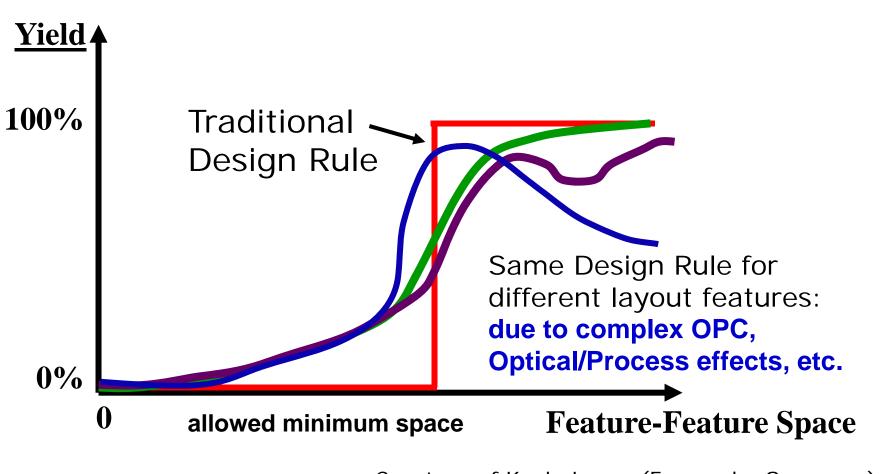

#### Yield vs. Design Rules at 32,28 and 22 nm

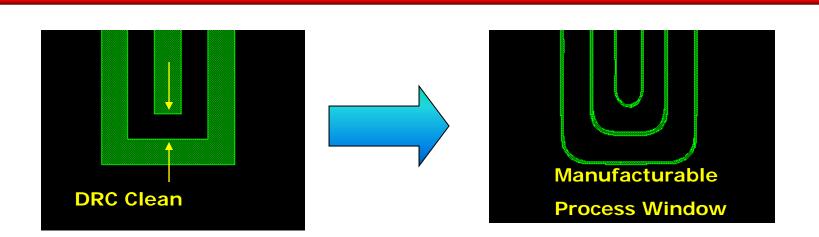

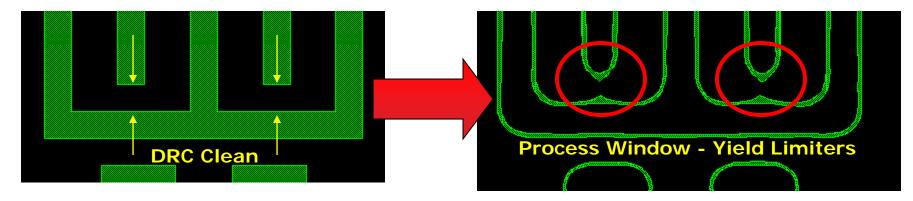

Design-Rules Compliance does NOT guarantee Yield due to: Non-Linearity Effects Induced by Sub-Wavelength Fabrication. Furthermore OPC cannot fix all Yield Limiters configurations

## DFM – Enabling First-Silicon-Success

# Physical Layout Re-Design (32,28nm)

#### Long History of Lithography and Layout Co-Optimization

130nm SRAM Traditional layout

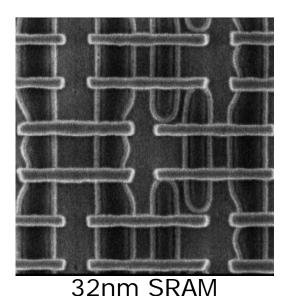

45nm SRAM

90nm SRAM Uni-directional poly

**GLOBAL**FOUNDRIES

Dr. Jongwook Kye Strategic Lithography GLOBLFOUNDRIES

65nm SRAM Uni-directional active

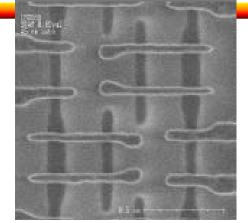

22nm SRAM Higher NA immersion

Immersion, uniform poly CD10/20/2009Luigi Capoo

Luigi Capodieci, Ph.D. - DFM Director - GLOBALFOUNDRIES

Double patterning

Extreme Patterning Solutions 14

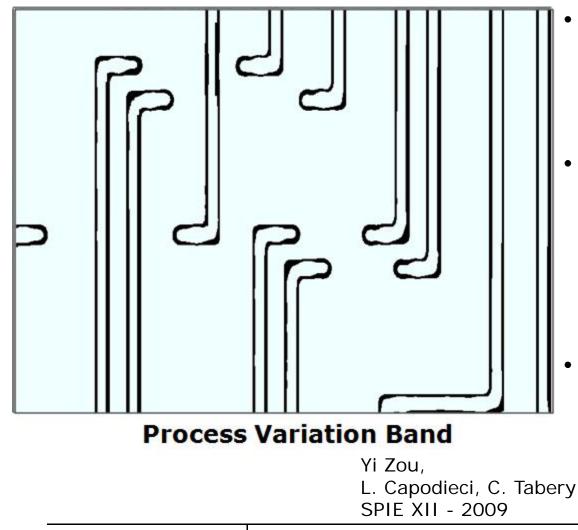

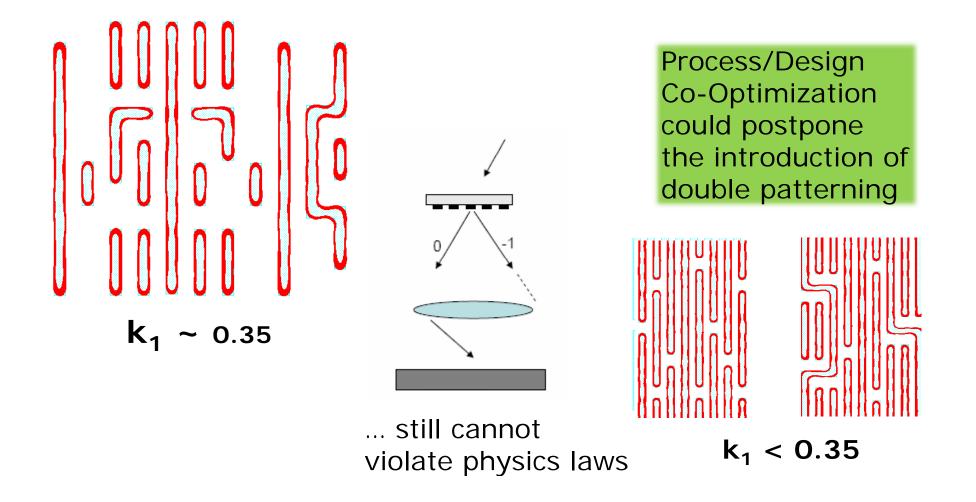

## Bridge to 22nm: Process-Aware Design

## Mask Optimization (MO):

Inverse Lithography Model-Based Assist Features

- Various inverse lithography methods for model-based AF insertion have been proposed

- Given a pixel-based objective function, inverse lithography synthesizes mask shapes, based on optical image analysis

- The mask synthesis process generates "corrected" shapes surrounded by AF shapes, both positive and negative

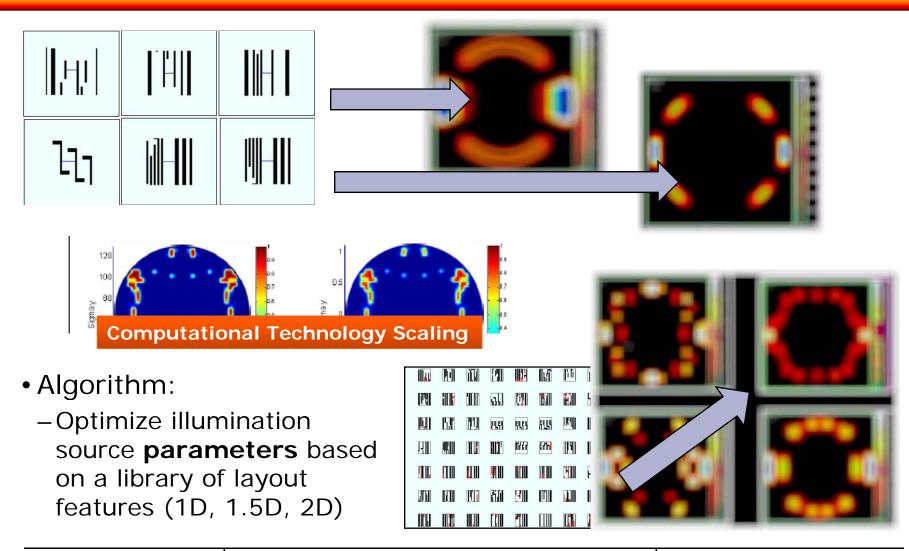

#### Source Optimization (SO)

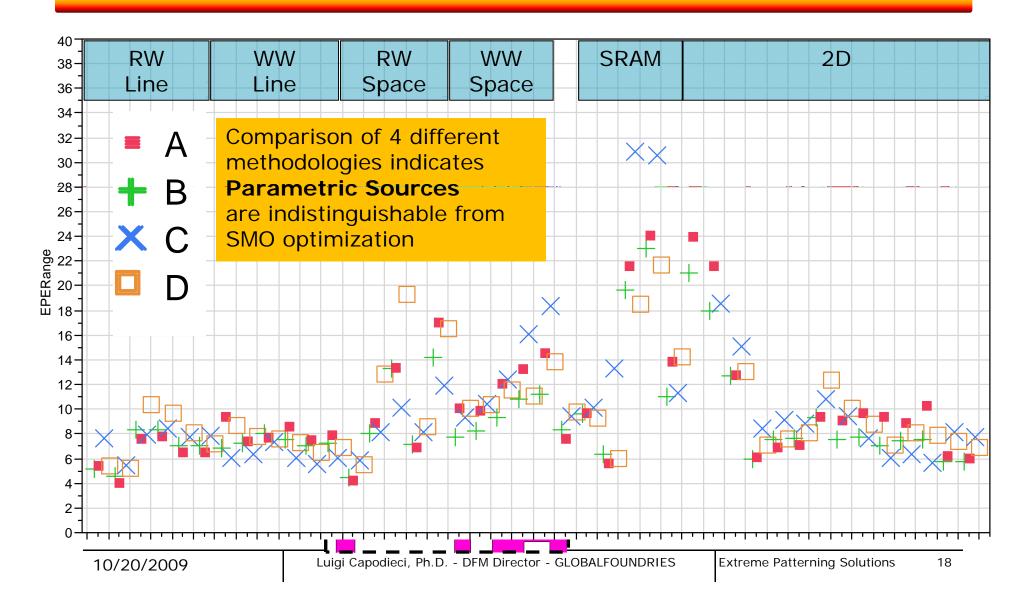

# Simultaneous Source Mask Optimization SMO: Theory and Reality

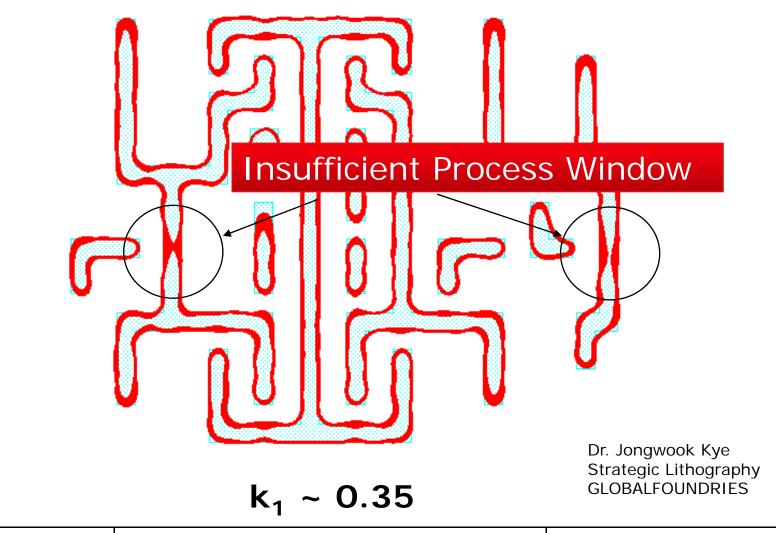

#### Limitations of RET and SMO at 22nm

#### DFM + Restricted Design Rules at 22nm

GLOBALFOUNDRIES

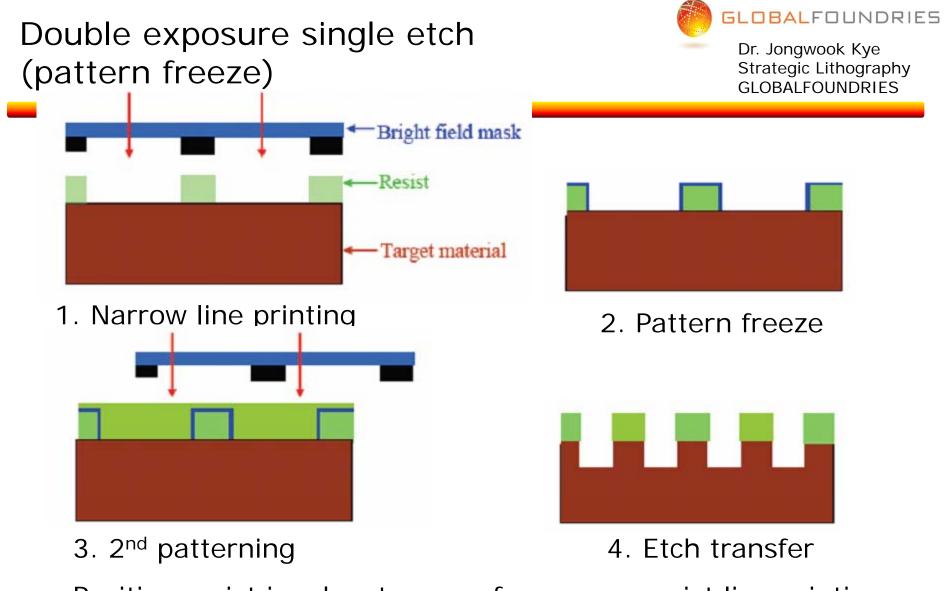

#### Double Exposure/Double Patterning at 20nm and below

| Increasing Process Complexity                |                                                             |                                |

|----------------------------------------------|-------------------------------------------------------------|--------------------------------|

| One Film<br>One Etch                         | Two Films<br>One Etch                                       | Two Films<br>Two Etches        |

| CEL<br>'Memoryless Resist'<br>'New Concepts' | Resist Stabilization<br>-Pattern Freezing<br>-Dual Solvents | Conventional<br>Resist Process |

| Increasing Resist Materials Complexity       |                                                             |                                |

Positive resist is advantageous for narrow resist line printing

Positive resist pattern freeze is challenging

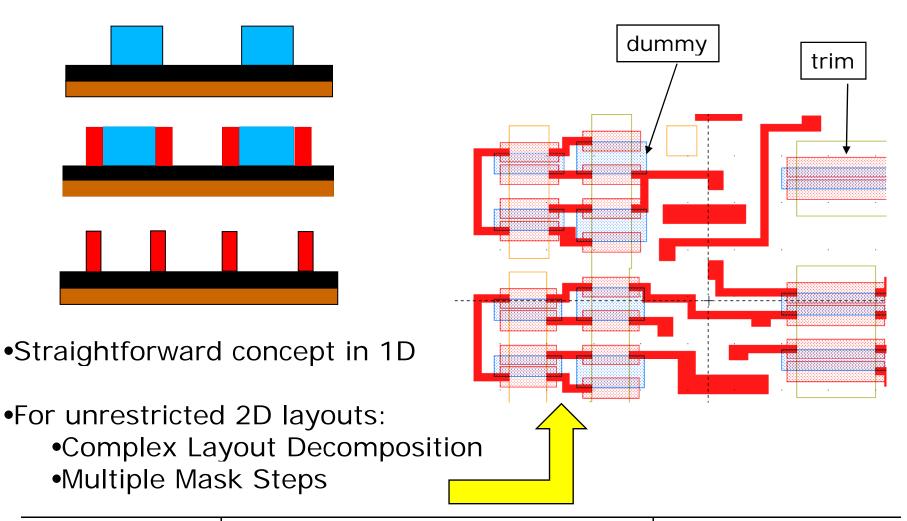

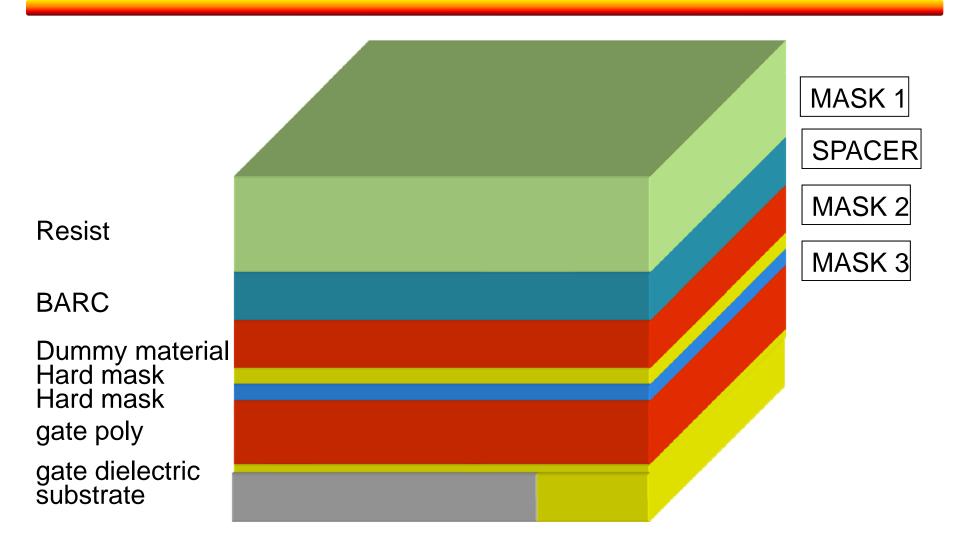

#### Sidewall Image Transfer (SIT) Self-Aligned Double Patterning (SADP)

#### Spacer-defined patterning: Complex Process Integration

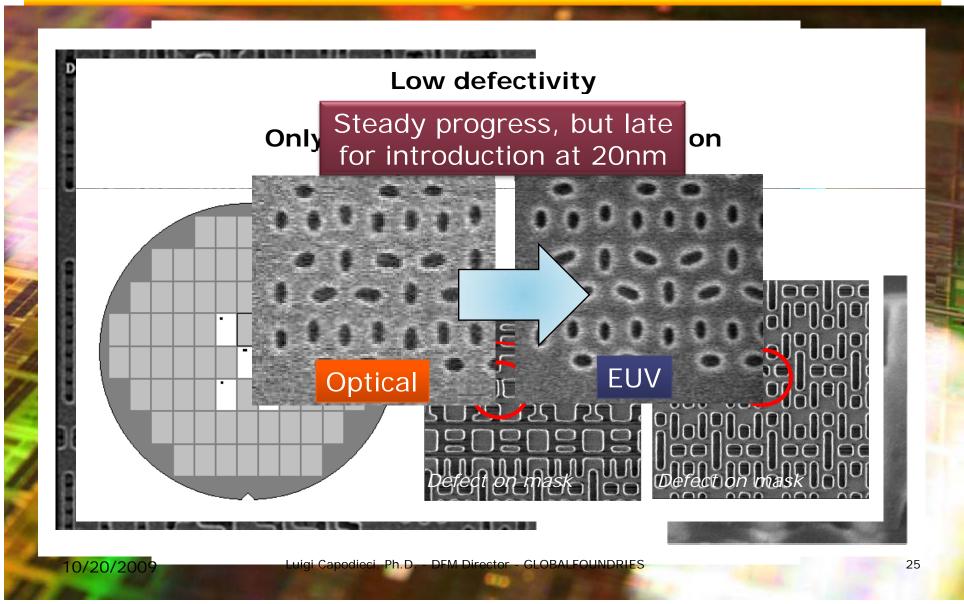

# 1<sup>st</sup> Full-Chip EUV Demo: GF/AMD & IBM

#### Summary: Current "State" of Patterning

- Extreme RET (DFM, SMO, ...)

- -Viable to 22nm

- Double Patterning (or Multi-Mask Patterning)

Needed at 20nm, issues of cost and process complexity

- EUV:

- -Steady progress, but late for introduction at 20nm

- Nano-Imprint

- -Problems: Defectivity, Overlay, Throughput

- Directed Self-Assembly

- -Still in "demo" phase. Can DNA scaffolding provide a breakthrough?

- Maskless

- -Might work for low-volume, issues of low throughput

## Acknowledgments

Jongwook Kye, Ryoung-han Kim, Tom Wallow, Harry Levinson, Rich Klein, Norma Rodriguez, Marilyn Wright, Rolf Seltmann, Cyrus Tabery, Sarah McGowan, Carl Babcock, Chris Spence, Yi Zou, Jie Yang, Vito Dai, Ethan Cohen, Uwe Hahn, Mark Craig, JR Zhou, Ed Roseboom, Stefan Roling, FAB1/A/B, Norman Chen, Chidam Kallingal, Jason Cain, ...

... and many, many others at GLOBALFOUNDRIES and AMD

10/20/2009