Empowered by Innovation NEC

### **MRAM : Materials and Devices**

# Current-induced Domain Wall Motion High-speed MRAM

N. Ishiwata

**NEC Corporation**

A portion of this study was supported by NEDO.

#### Outline

#### Introduction

- Positioning and direction of MRAM

- High speed MRAM cell

- Domain wall motion cell for high speed MRAM

- Device structure and materials

- Writing properties and memory operation

## Summary

#### **Comparison of novel and conventional memories**

|                                  | MRAM                              | FeRAM                           | PRAM                           | FLASH                          | SRAM                              | DRAM                              |

|----------------------------------|-----------------------------------|---------------------------------|--------------------------------|--------------------------------|-----------------------------------|-----------------------------------|

| Mechanism                        | Magnetic<br>Tunnel<br>Junction    | Ferro-<br>electric              | Phase<br>change                | Floating<br>gate               | Transistor                        | Capacitor                         |

| Non-volatile                     | Ο                                 | ο                               | О                              | О                              | ×                                 | ×                                 |

| Endurance                        | Unlimited<br>(>10 <sup>15</sup> ) | Limited<br>(<10 <sup>13</sup> ) | Limited<br>(<10 <sup>9</sup> ) | Limited<br>(<10 <sup>6</sup> ) | Unlimited<br>(>10 <sup>15</sup> ) | Unlimited<br>(>10 <sup>15</sup> ) |

| Access time                      | Very Fast<br>(~10ns)              | Fast<br>(50~100ns)              | Medium<br>(>100ns)             | Fast (read)<br>Slow (write)    | Very fast<br>(~10ns)              | Fast<br>(~50ns)                   |

| Refresh                          | No                                | No                              | No                             | No                             | No No                             |                                   |

| Cell size                        | Medium                            | Large                           | Small                          | Very Small                     | y Small Large                     |                                   |

| Low voltage                      | 0                                 | 0                               | 0                              | Δ                              | 0                                 | 0                                 |

| High<br>temperature<br>operation | 0                                 | ×                               | ×                              | Δ                              | ο                                 | Δ                                 |

| Application                      | Work<br>memory                    | Work<br>memory?                 | Storage                        | Storage                        | Work<br>memory                    | Work<br>memory                    |

MRAM has great potential for use as non-volatile working memory.

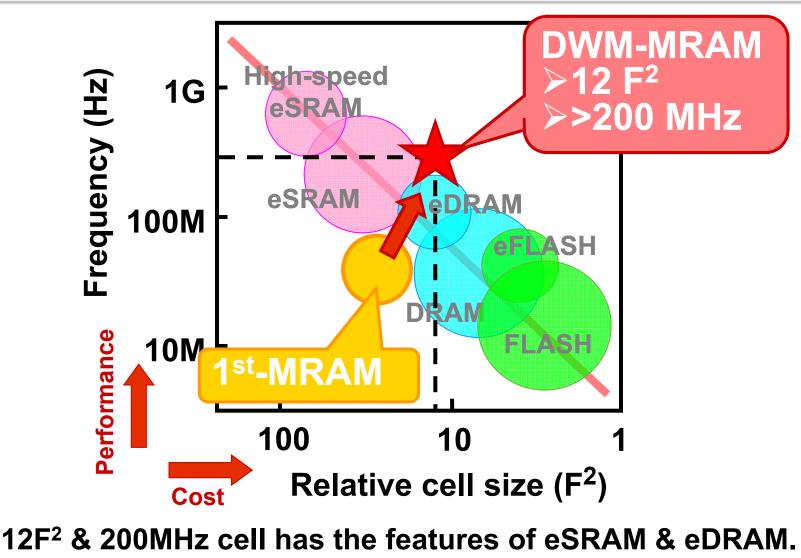

#### **DWM-MRAM** cell is located at ...

Very useful for future high-speed embedded memory in SoC.

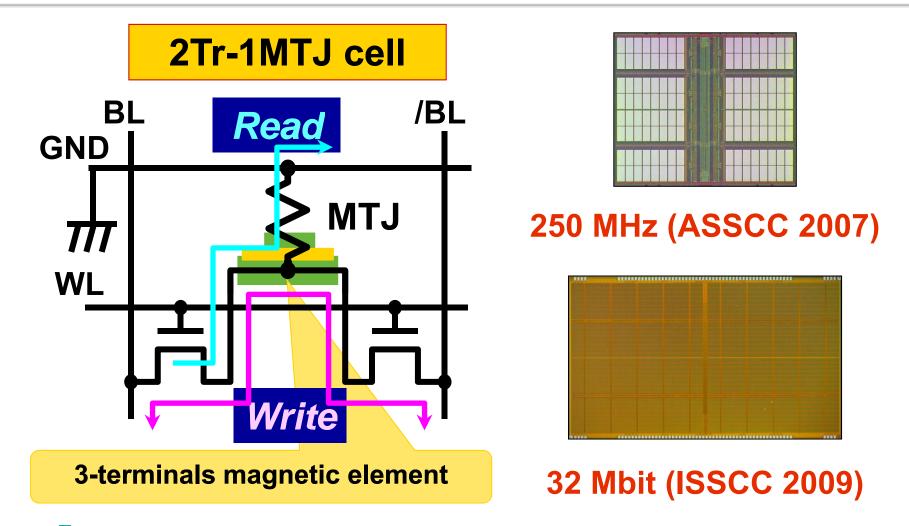

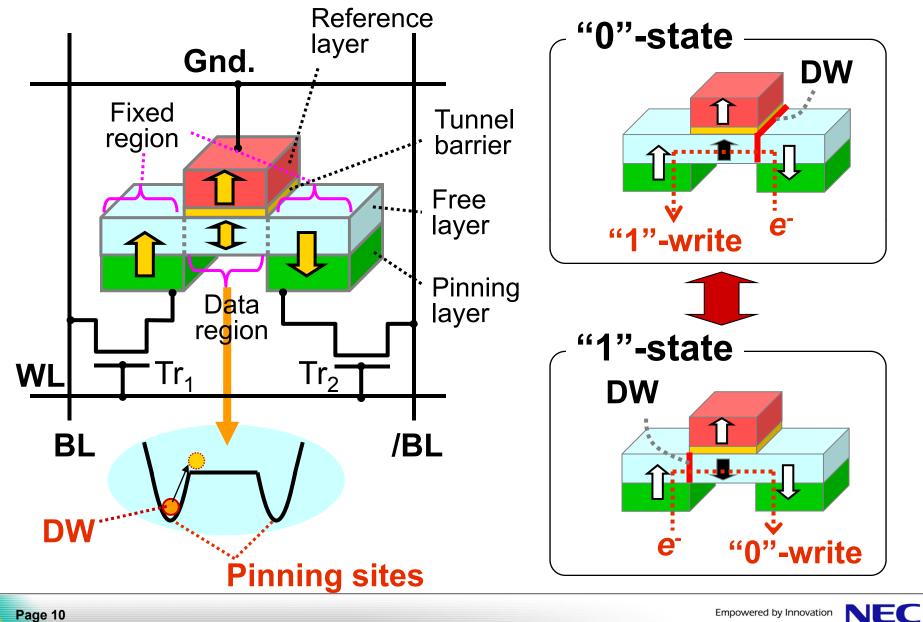

#### 2Tr-1MTJ cell for high-speed MRAM operation

No problem with either write disturbance or read one ⇒ Great advantage for high-speed operation

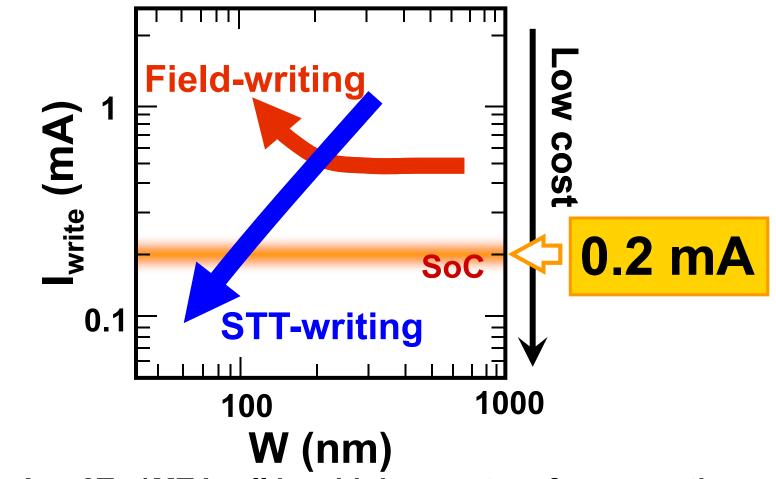

#### **Key issue : Reduction of write-current (I<sub>write</sub>)**

<0.2 mA  $\Rightarrow$  2Tr-1MTJ cell has higher cost performance than conventional memories used in SoC.

Spin-transfer torque switching is promising for lowering write-current.

#### Conventional Spin transfer torque switching

F.J.Albert et al., Appl. Phys. Lett., 77-23, 3809, 2000.

#### Current-induced domain wall motion (DWM)

- A.Yamaguchi et al., Phys. Rev. Lett. 92, 077205, 2004.

- NiFe (in-plane)

- M. Yamanouchi et al., NATURE, 428, P.539, 2004.

- GaMnAs (perpendicular)

- Suitable for 2Tr-1MTJ cell

- Scalable write-current & write-speed

- Sufficient thermal stability without write current increase

- Suppression for read disturbance & tunneling barrier damage in write process

- CMOS process compatibility

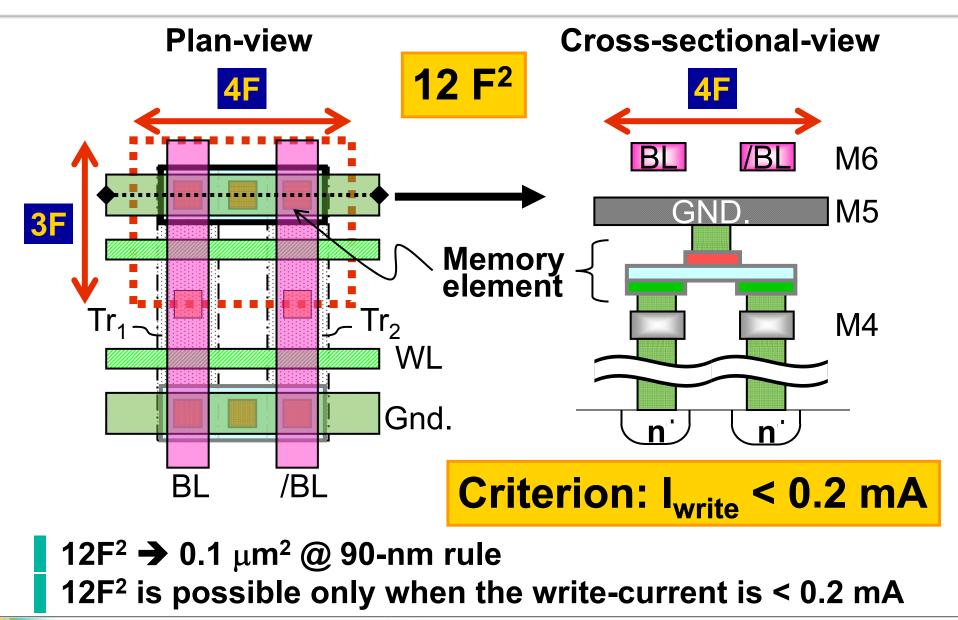

#### Minimum cell layout for 2Tr-1MTJ DWM cell

#### **Device structure for minimum cell layout**

Page 10

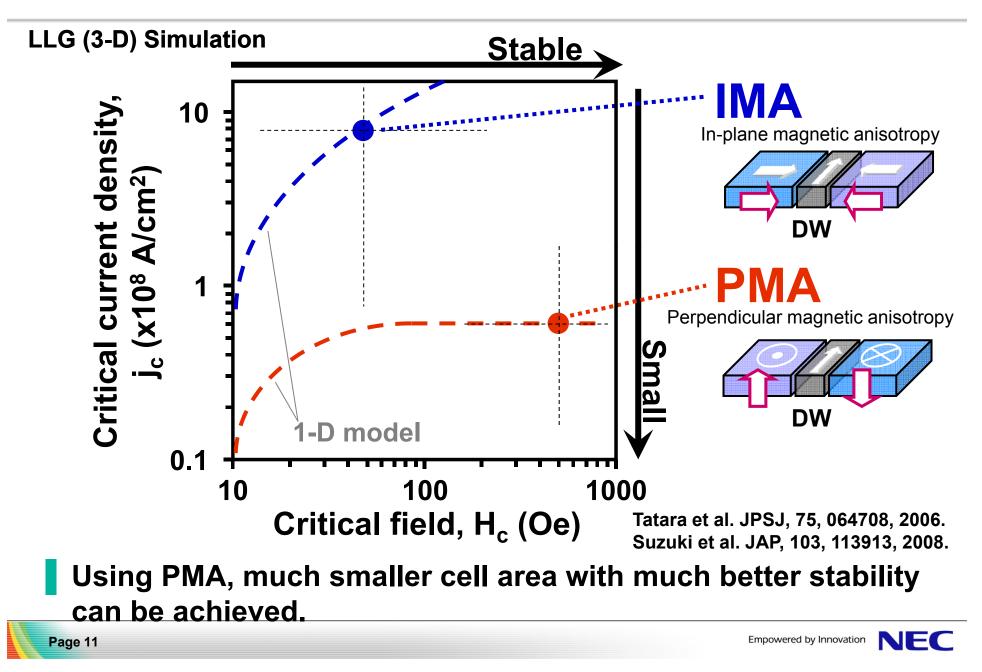

#### What kind of material should be chosen ?

#### **DWM** materials

| Material             | Anisotropy    | Temp.<br>(K) | Minimum<br>J <sub>th</sub> (A/m²) | Pinning<br>field (Oe) | Velocity<br>(m/sec.) |

|----------------------|---------------|--------------|-----------------------------------|-----------------------|----------------------|

| [Co/Ni] <sub>N</sub> | Perpendicular | R.T.         | 0.3x10 <sup>12</sup>              | 200                   | 60                   |

| [Co/Pt] <sub>N</sub> | Perpendicular | R.T.         | 1.8x10 <sup>12</sup>              | 500                   | -                    |

| CoCrPt               | Perpendicular | R.T.         | 1.0x10 <sup>12</sup>              | 500                   | -                    |

| GaMnAs               | Perpendicular | 100          | 8.0x10 <sup>8</sup>               | 40                    | 22                   |

| NiFe                 | In-plane      | R.T.         | 1.0x10 <sup>12</sup>              | 5                     | 110                  |

Co/Ni is the best material for DWM, because of its small J<sub>th</sub> with large pinning field and high velocity.

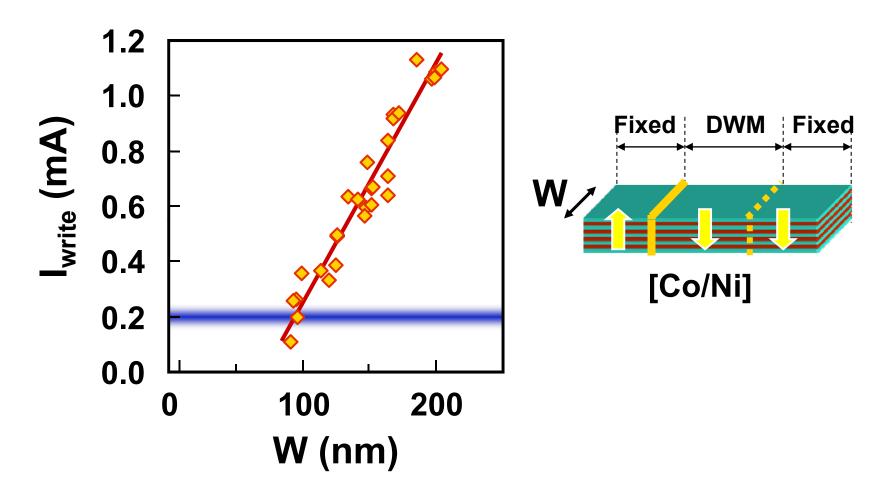

#### Write-current, I<sub>write</sub>

At less than 100 nm width, the write-current becomes less than 0.2 mA.  $\Rightarrow$  The most important criterion is satisfied.

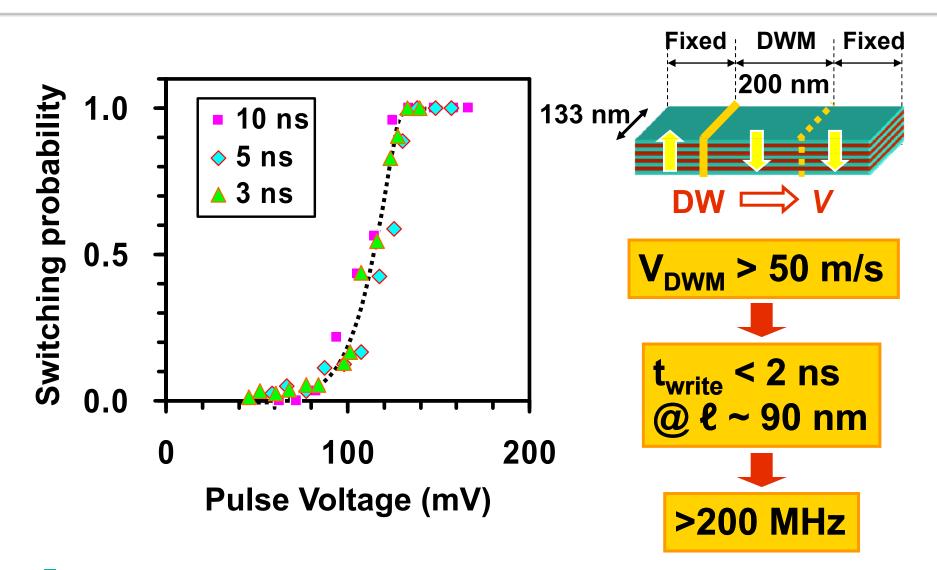

#### Write-time, t<sub>write</sub>

More than 200 MHz operation is promising.

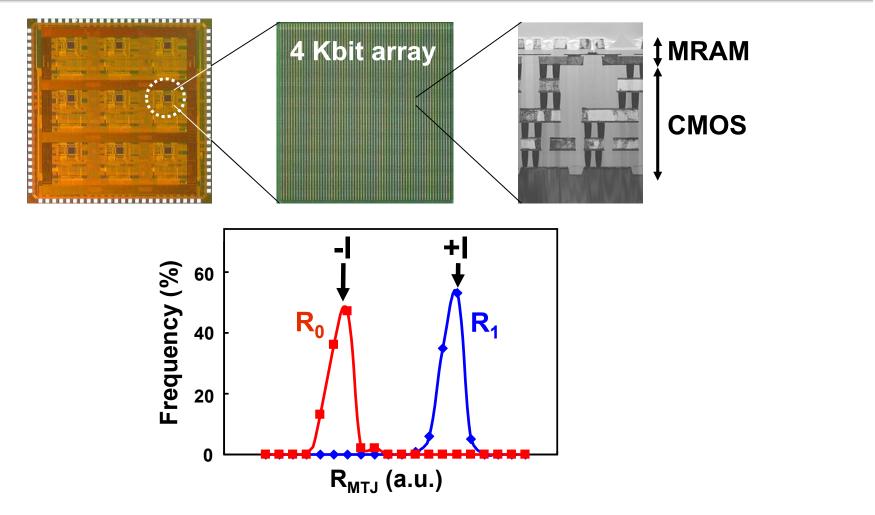

#### **Memory operation : 4 Kbit array**

The two resistance states of the MTJ are clearly separated. The change of resistance is consistent with current direction.

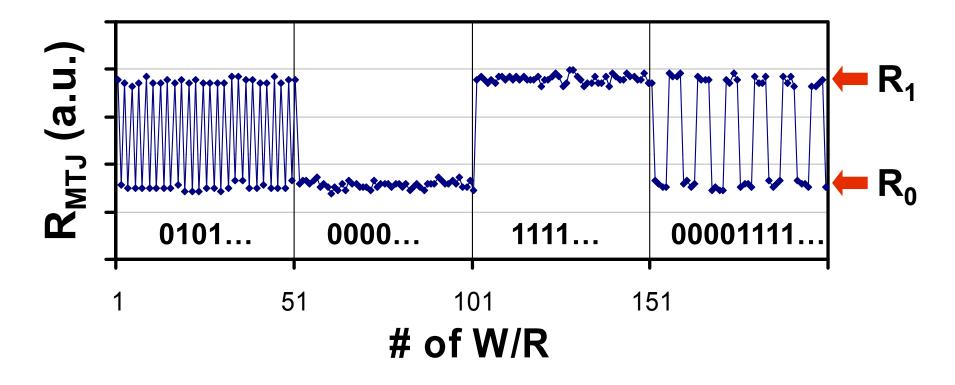

#### **Repeat test for write and read operation**

Good reproducible switching and overwrite properties are confirmed.

#### Summary

#### DWM MRAM with 2Tr-1MTJ high-speed cell

- 12 F<sup>2</sup> (0.1 μm<sup>2</sup> @ 90 nm rule), >200 MHz

- Scalable write-current & write-speed with sufficient thermal stability

- 4 kbit memory array operation has been demonstrated

# Co/Ni multilayer film with perpendicular magnetic anisotropy is the answer for DWM MRAM

Empowered by Innovation NEC

# Thank you