Source: When will computer hardware match the human brain? Hans Moravec, 1998

SRC/NSF/A\*STAR Forum

# **Memories**

- Memory Size, Density, Performance & Cost

- Existing Memories:

- Registers

- Cache, SRAM

- Primary Memory, DRAM

- Secondary Memory, NAND, FCRAM, SSD, Disc

- Cross-Point (or Bar) Memory & Probe-Based Memory

- Memory/Processor ("single" chip multi-thread, multi-core processor)

- Many Challenges Ahead

October 20-21, 2009

SRC/NSF/A\*STAR Forum

### Anticipated Memory Hierarchy Capacities and Latencies in 2016

| <b>Technology</b><br>SRAM<br>DRAM<br><i>Flash</i><br>Magnetic Disk                                                                                                  | Access Time<br>0.5 – 5 ns<br>50 – 70 ns<br>~ 0.2 ms<br>5 – 20 ms | <b>\$ per GB</b><br>4000 – 10,000<br>100 – 200<br>~ 60<br>0.5 – 2 | <b>MB per \$</b><br>0.1 – 0.25<br>5 - 10<br><i>17</i><br>500 - 2000 | )                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|---------------------|

| <b>Type</b><br>Registers<br>Cache, SRAM<br>Primary Memor<br>Secondary Mer                                                                                           | •                                                                | Capacity<br>< 1 kB<br>< 16 MB<br>< 16 GB<br>> 100 GB              | Latency<br>~ 0.25 ns<br>~ 0.5 ns<br>~ 80 ns<br>~ 5 <i>ms</i>        | x1000<br>difference |

| <ul> <li>There is a difference in capacity and latency of about three orders of magnitude between the memory types</li> <li>3D Integration for Memories?</li> </ul> |                                                                  |                                                                   |                                                                     |                     |

| October 20-21, 2009 SRC/NSF/A*STAR Forum                                                                                                                            |                                                                  |                                                                   |                                                                     |                     |

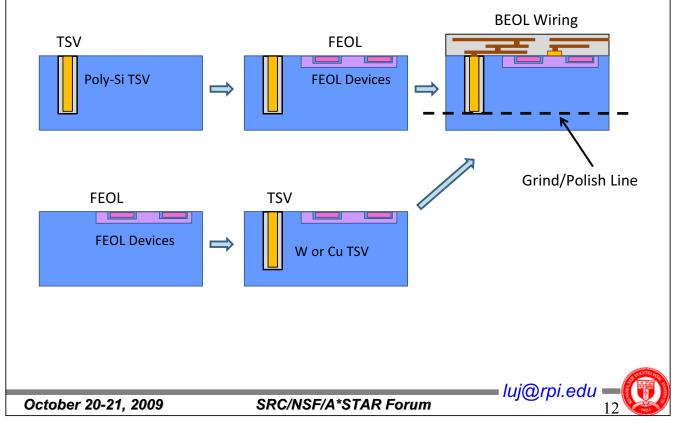

# FEOL and BEOL TSV Formation

### Wafer-Level 3D IC: Benefits, Challenges and Strategies

#### **Potential Benefits**

- Density/Capacity

- Wire Delay

- Bandwidth

- Power

- Material/Processing

- Functionality

- Packaging

- Cost

#### **Challenges**

- Thermal and Power

- Yield concerns

- Test methodology

- Infrastructures

- Equipment

- ECAD Design

- Standard

#### **Technology Strategies**

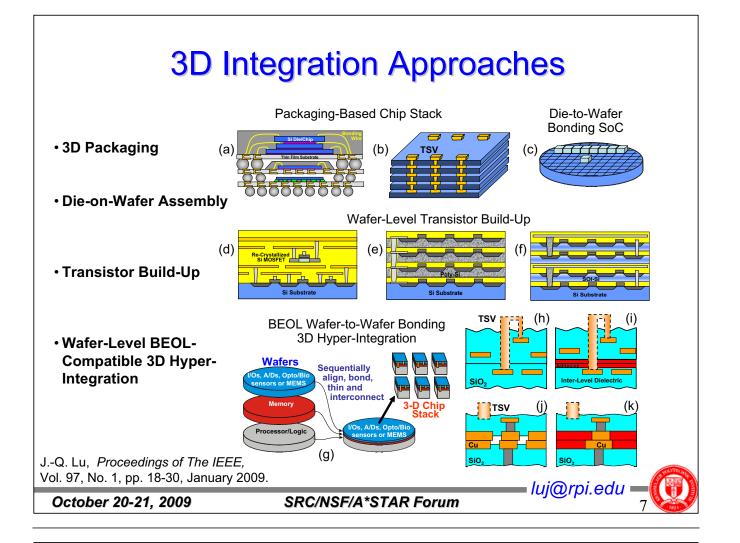

- Platform/Architecture

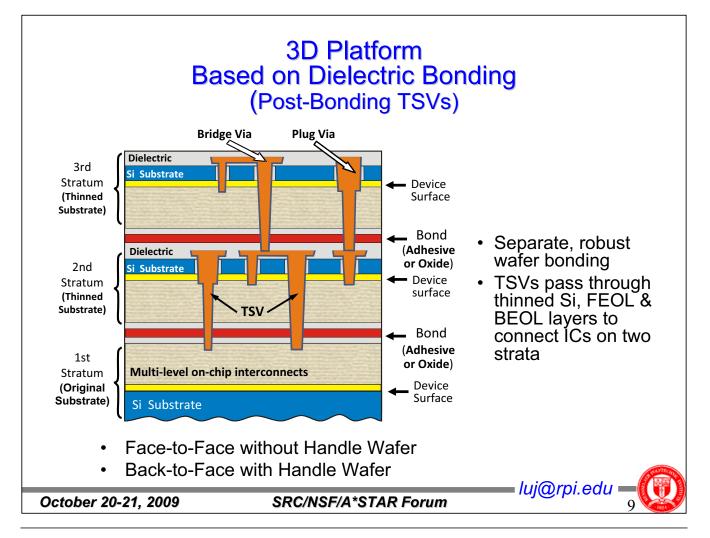

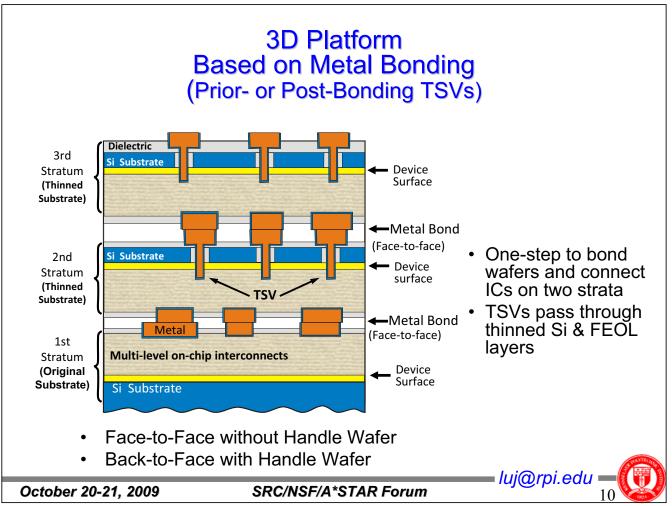

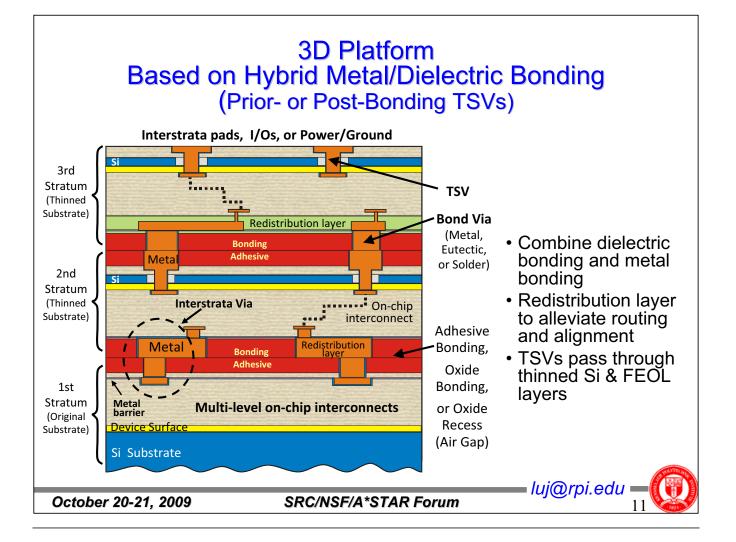

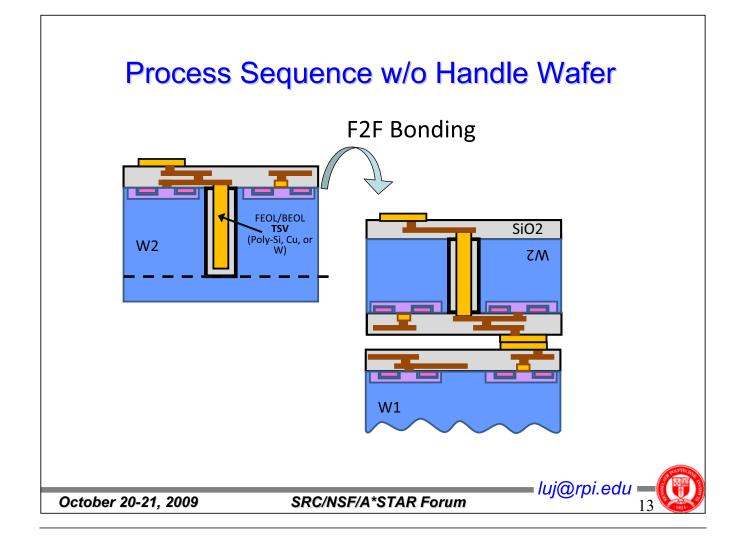

- Face-to-face vs face-to-back

- Via-first vs via-last

- Transistor build up vs. BEOL 3D

- Substrate

- SOI (Si-on-Insulator)

- Bulk Si

- Processing Technologies

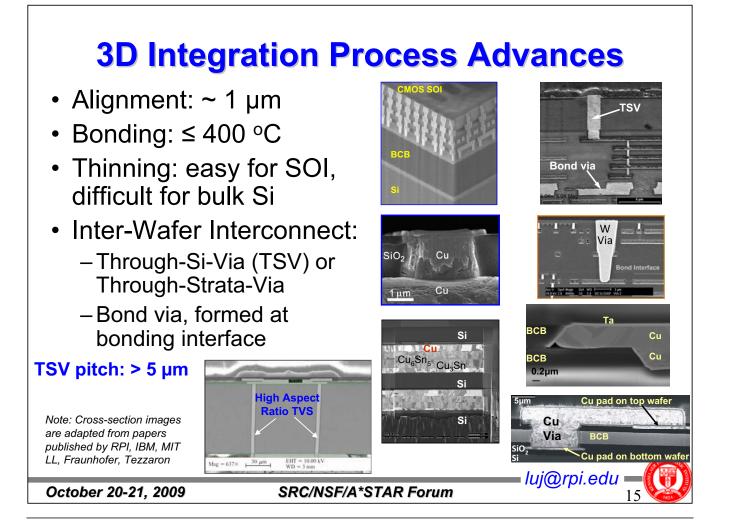

- Alignment

- Bonding

- Thinning

- Inter-wafer interconnect

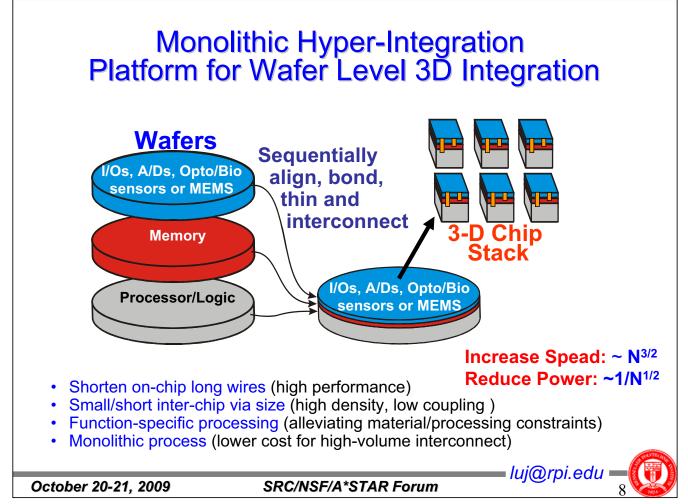

Eliminate the slower and higher-power off-chip buses to memory by replacing them with high-bandwidth and low-latency vertical interconnections

October 20-21, 2009

SRC/NSF/A\*STAR Forum

Iuj@rpi.edu 💻

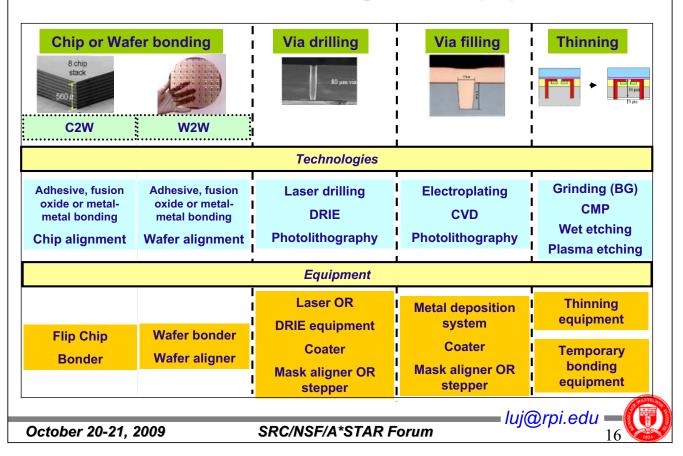

### **TSV 3D IC Technologies & Equipment**

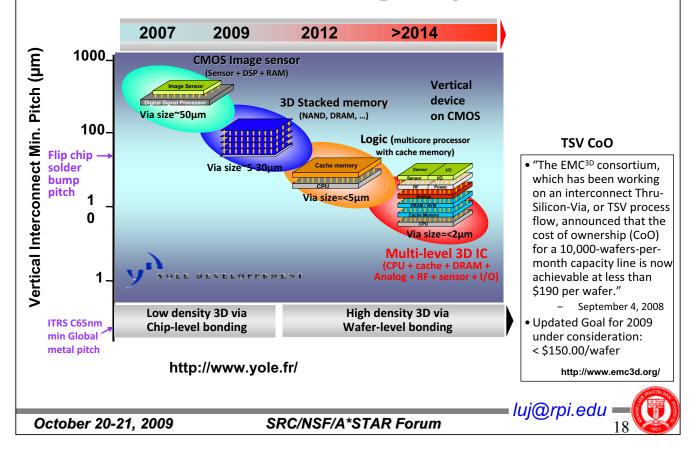

## **3D Market Timing Projections**

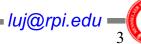

# **Suggestion of Research Areas**

- Basic research: materials, processing, reliability, thermal, modeling & design CAD tools

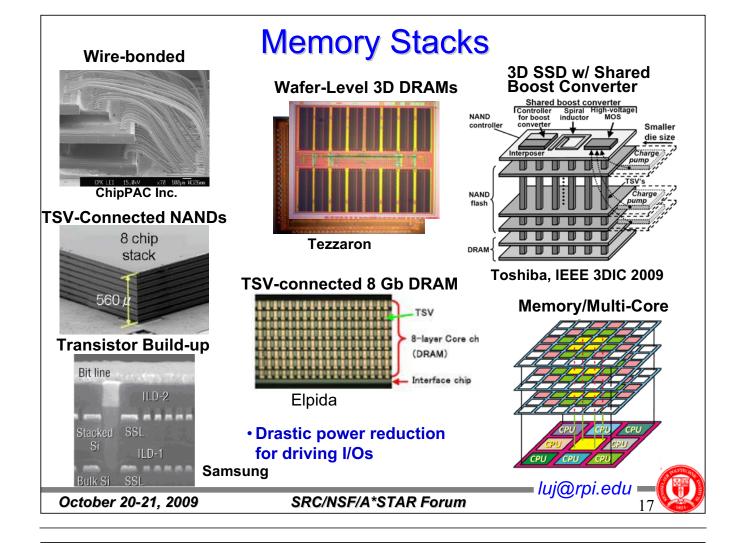

- Simulation and compact models for prediction of density, speed and energy of 3D memory stack

- Impact of TSV electric/magnetic/thermal performance and placement/routing?

- Impact of 3D integrated memories on μProcessor performance

- CPI beyond the memory wall?

- Do we need Network on Chip (NoC) for many core 3D systems with huge stacked memory?

- Algorithm & hierarchy for NEW 3D memory architectures

- Improve density, speed and energy, e.g., with separate strata of addressing, driving, or sensing circuitry?

- Allocate shared memory resources between multiple cores?

October 20-21, 2009

SRC/NSF/A\*STAR Forum

Iuj@rpi.edu 🗕