# **SRC 3D Summit**

Bob Patti, CTO

rpatti@tezzaron.com

Tezzaron Semiconductor

05/05/2011

Tezaron

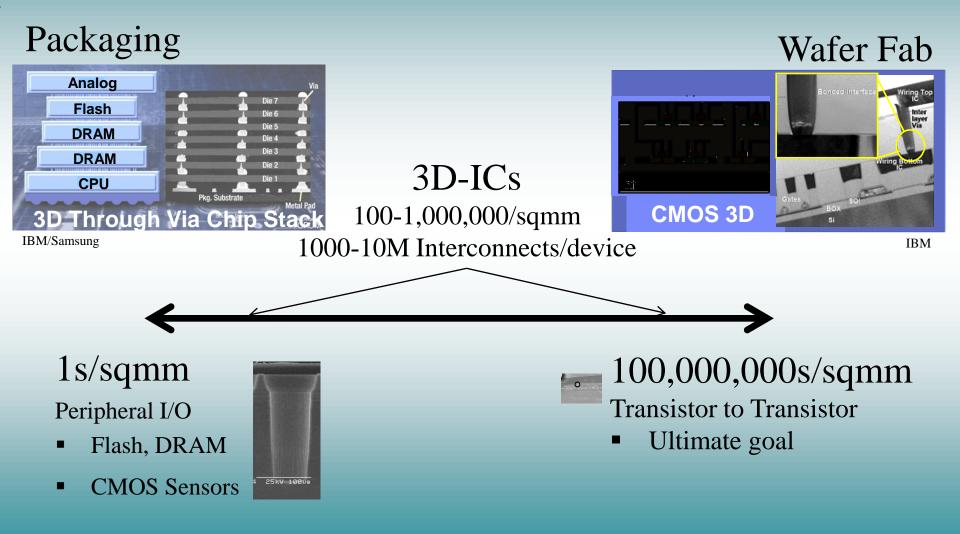

# **3D Stacking Approaches**

|                                                                                         | ching hppi va                                                      |                                     |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------|--|

| Chip Level                                                                              | Device Level                                                       | Wafer Level                         |  |

| <ul> <li>Ziptronix</li> <li>Vertical Circuits</li> <li>Elpida/Micron/Samsung</li> </ul> | • Stanford<br>• Besang                                             | • Infineon/IBM<br>• RPI<br>• ZyCube |  |

| <image/> <image/> <image/> <image/> <image/>                                            | <section-header><section-header></section-header></section-header> | <image/>                            |  |

| ~                                                                                       |                                                                    |                                     |  |

Tezzaron Semiconductor

Tezaron

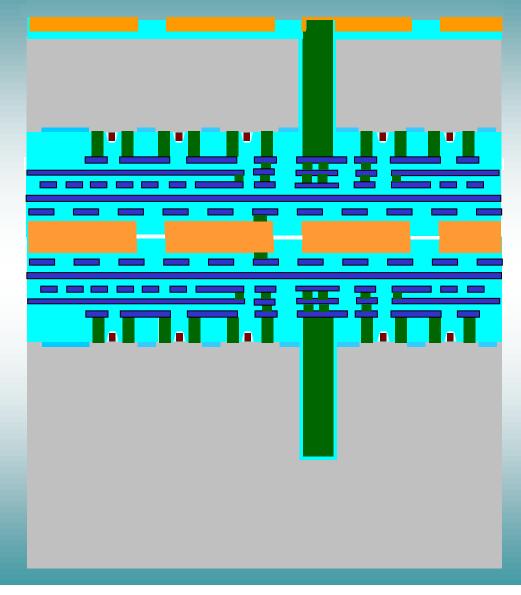

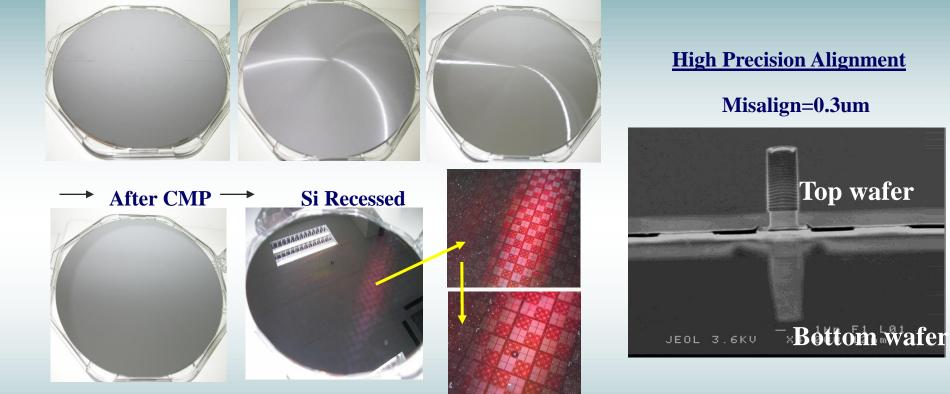

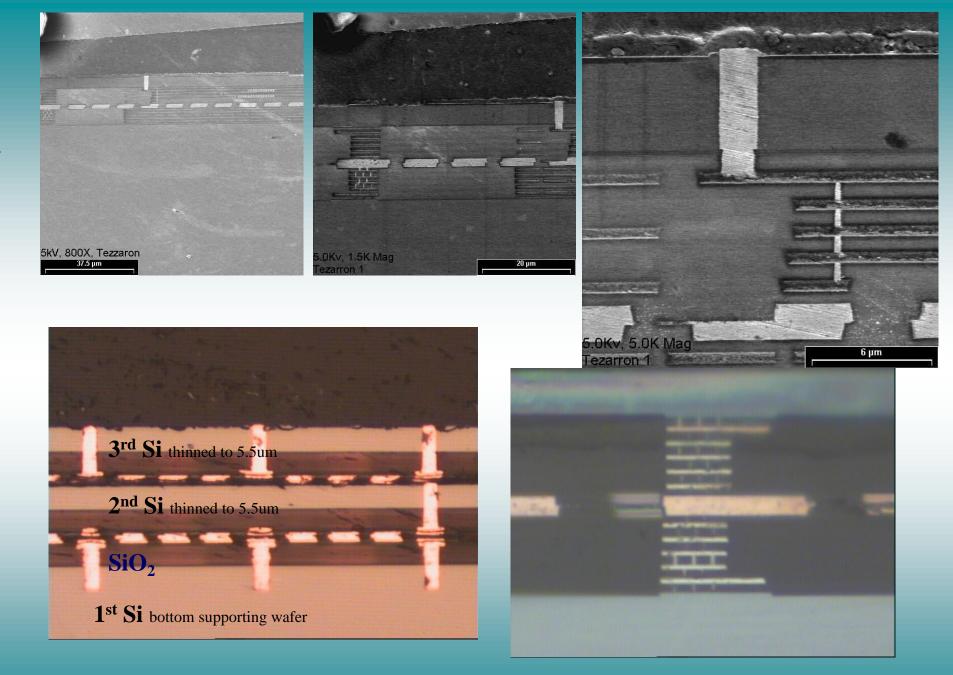

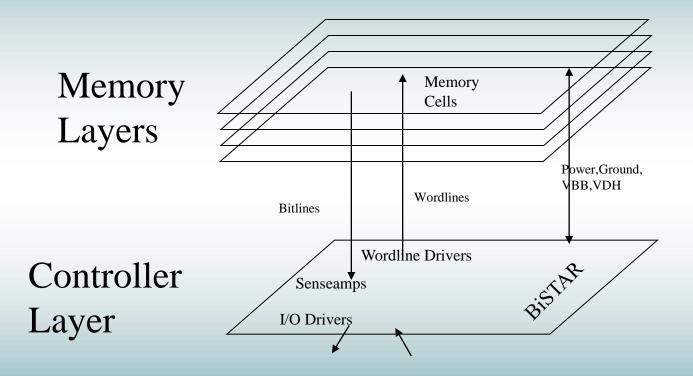

### **A Closer Look at Wafer-Level Stacking**

## Next, Stack a Second Wafer & Thin:

#### **Stacking Process Sequential Picture**

Two wafer Align & Bond → Course Grinded → Fine Grinded

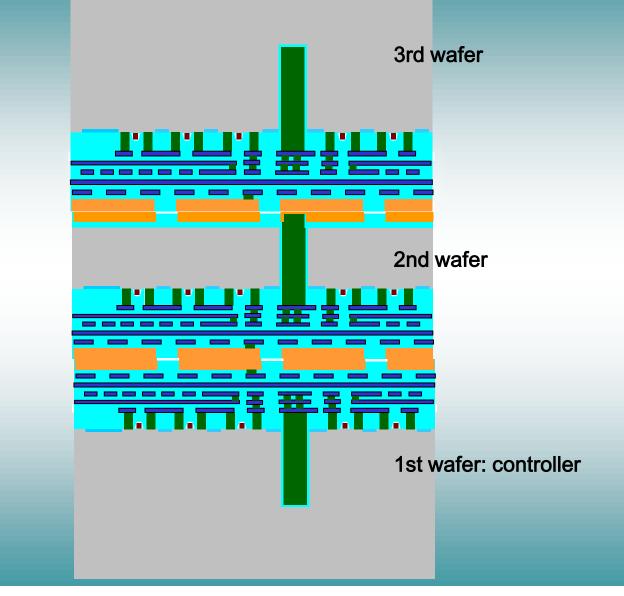

#### Then, Stack a Third Wafer:

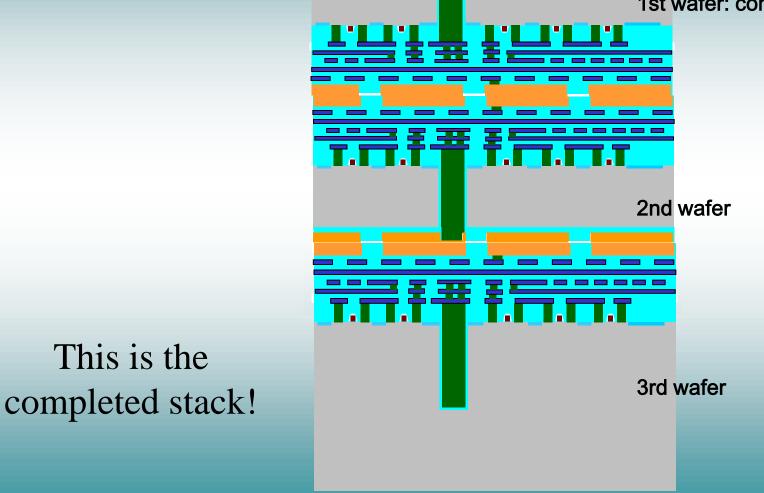

## Finally, Flip, Thin & Pad Out:

1st wafer: controller

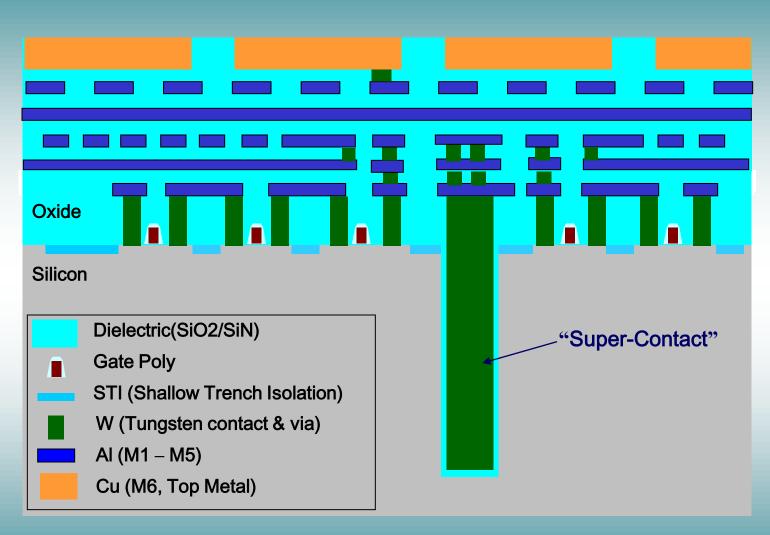

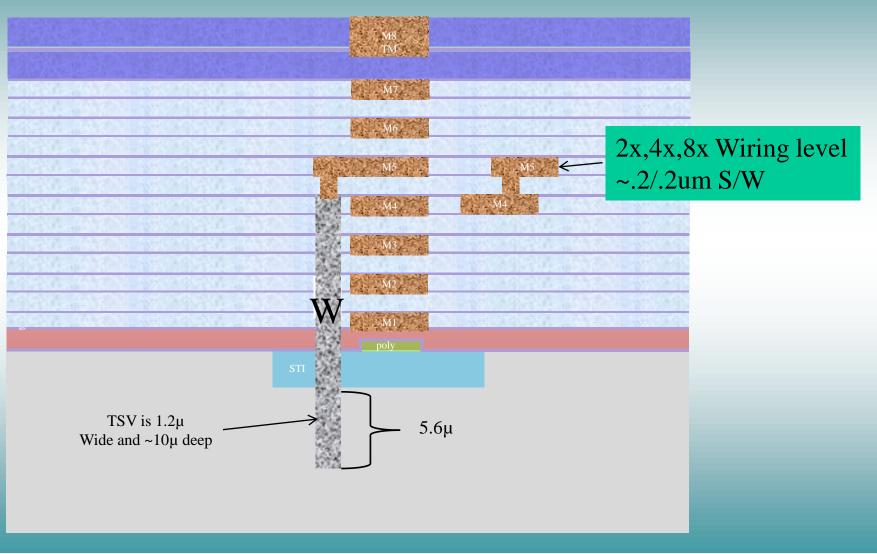

### **3D Interconnect Characteristics**

|                               | SuperContact <sup>™</sup><br>I<br>200mm<br>Via First, FEOL | SuperContact <sup>TM</sup><br>II<br>300mm<br>Via First, FEOL | SuperContact <sup>™</sup><br>III<br>200mm<br>Via First, FEOL | SuperContact <sup>TM</sup><br>4<br>200mm<br>Via First, FEOL | Bond Points         |

|-------------------------------|------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|---------------------|

| Size<br>L X W X D<br>Material | 1.2 μ X 1.2 μ<br>X 6.0μ<br>W in Bulk                       | 1.6 μ X 1.6 μ<br>X 10.0μ<br>W in Bulk                        | 0.85 μ X 0.85 μ<br>X 10μ<br>W in Bulk                        | 0.40 μ X 0.40 μ<br>X 2μ<br>W in SOI                         | 1.7 μ X 1.7 μ<br>Cu |

| Minimum<br>Pitch              | <2.5 μ                                                     | <3.2 μ                                                       | 1.75 μ                                                       | 0.8 μ                                                       | 2.4 μ<br>(1.1 μ)    |

| Feedthrough<br>Capacitance    | 2-3fF                                                      | 6fF                                                          | 3fF                                                          | 0.2fF                                                       | <<                  |

| Series<br>Resistance          | <1.5 Ω                                                     | <1.8 Ω                                                       | <3 Ω                                                         | <1.5 Ω                                                      | <                   |

#### **Pitch and Interconnect**

- SuperContact<sup>TM</sup> is 500f<sup>2</sup> (including spacing)

- Face to face is 350f<sup>2</sup> (including spacing)

- Chip on wafer I/O pitch is 35,000f<sup>2</sup>

- Standard cell gate is 200 to 1000f<sup>2</sup>

- 3 connections

- Standard cell flip-flop is 5000f<sup>2</sup>

- 5 connections

- 16 bit sync-counter is  $125,000f^2$

- 20 connections

- Opamp is 300,000f<sup>2</sup>

- 4 connections

f<sup>2</sup> is minimum feature squared

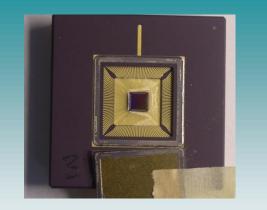

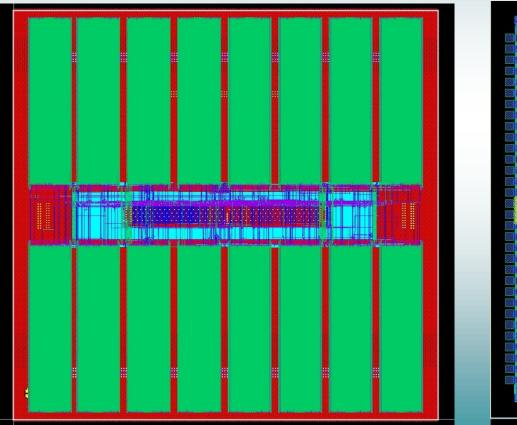

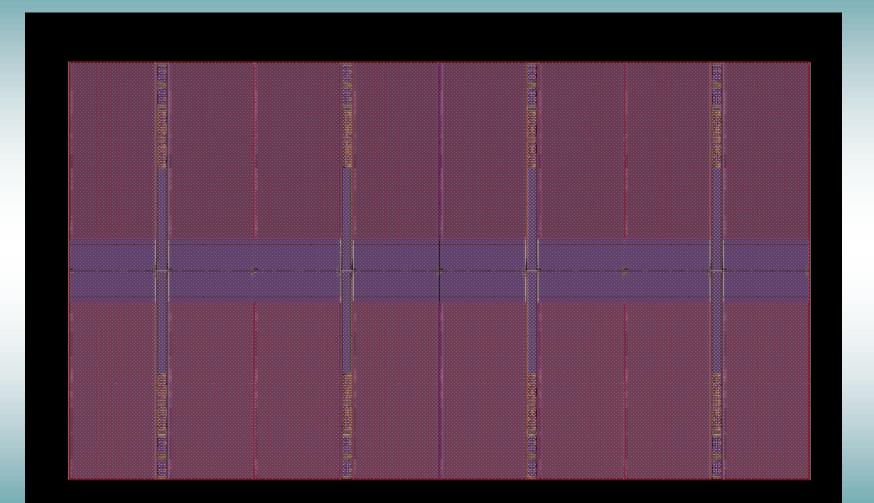

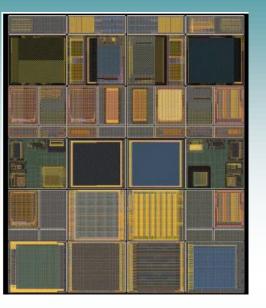

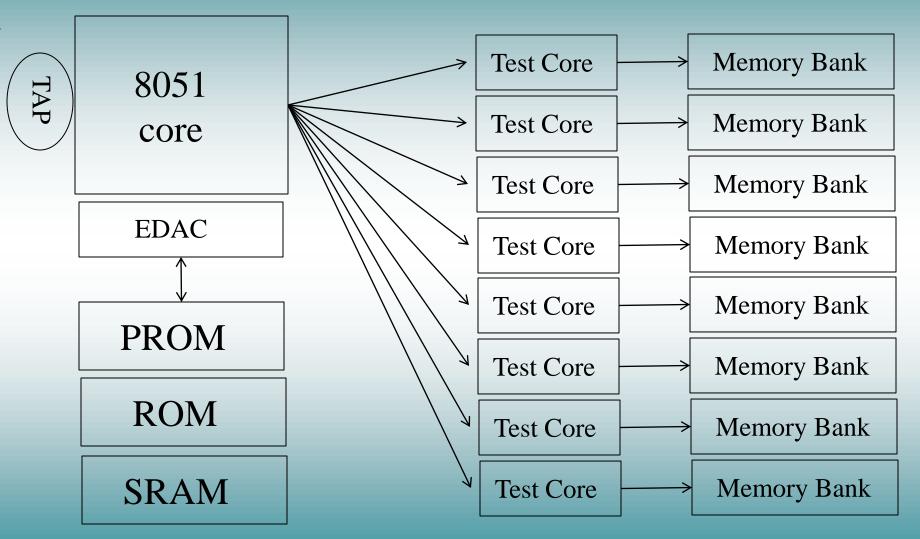

## R8051/Memory

5X Performance 1/10<sup>th</sup> Power

Dist:

Cmd:

8

Help

| Q                                            |                                          |                                                  |

|----------------------------------------------|------------------------------------------|--------------------------------------------------|

| €< 0                                         |                                          |                                                  |

| S. HA                                        |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              |                                          |                                                  |

|                                              | ĨĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢĊŢŢ |                                                  |

|                                              |                                          |                                                  |

| <pre>mouse L: mouseSingleSelectPt &gt;</pre> | M: mousePopUp()                          | R: hiZoomAbsoluteScale(hiGetCurrentWindow() 0.9) |

#### New Apps – New Architectures

####

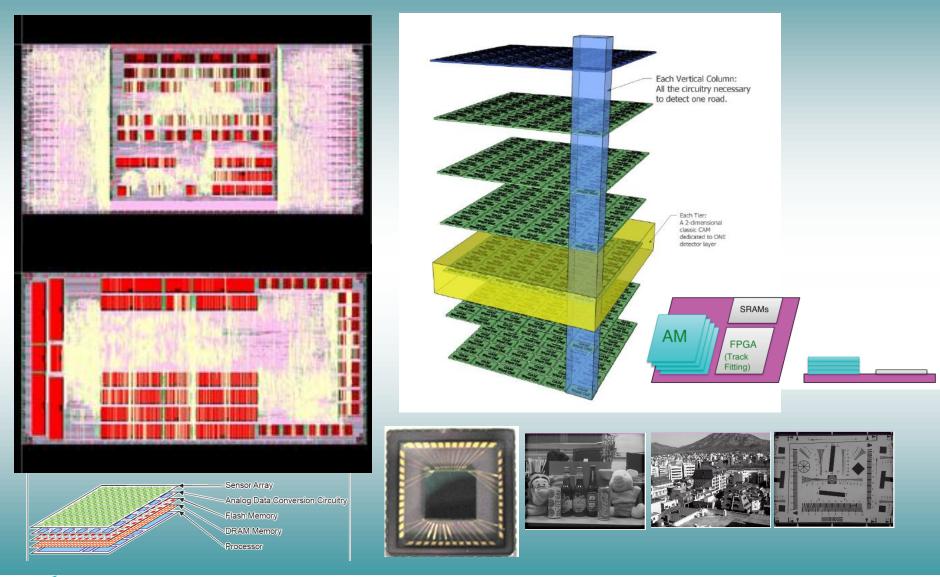

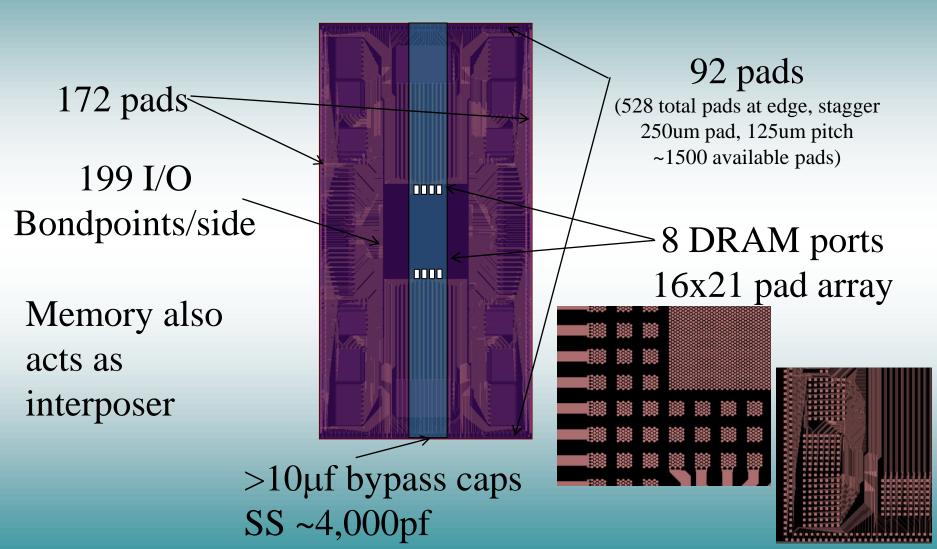

#### "Dis-Integrated" 3D Memory

- 1-4Gb

- 16 Ports x 128bits (each way)

- @1GHz

- CWL=0 CRL=2 SDR format

- 7ns closed page access to first data (aligned)

- <20ns full cycle memory time</li>

- 288GB/s data transfer rate

- Max clk=1.6GHz

- Internally ECC protected, Dynamic self-repair, Post attach repair

- 115C die full function operating temperature

- JTAG/Mailbox test&configuration

- Power -40%

- Density x4++

- Performance +300%

- Cost -50%

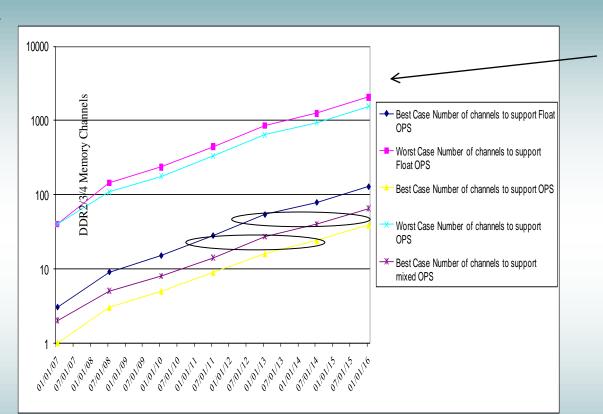

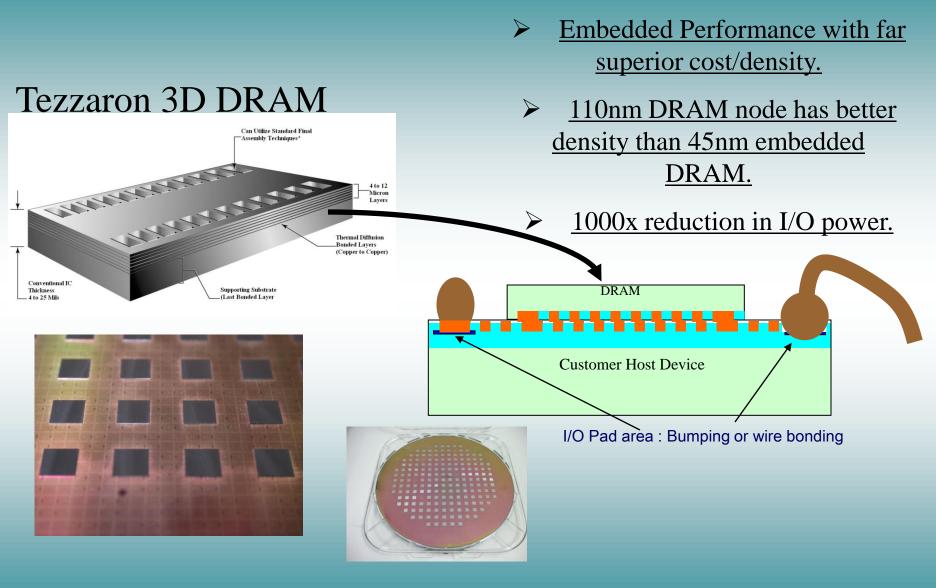

#### **Main Memory Power Cliff**

DDR3 ~40mW per pin 1024 Data pins →40W 4096 Data pins →160W Die on Wafer ~24uW per pin

#### **The Industry Issue**

To continue to increase CPU performance, exponential bandwidth growth required.

More than 200 CPU cycles of delay to memory results in cycle for cycle CPU stalls.

▶16 to 64 Mbytes per thread required to hide CPU memory system accesses.

No current extension of existing IC technology can address requirements.

Need 50x bandwidth improvement. Need 10x better cost model than embedded memory.

Memory I/O power is running away.

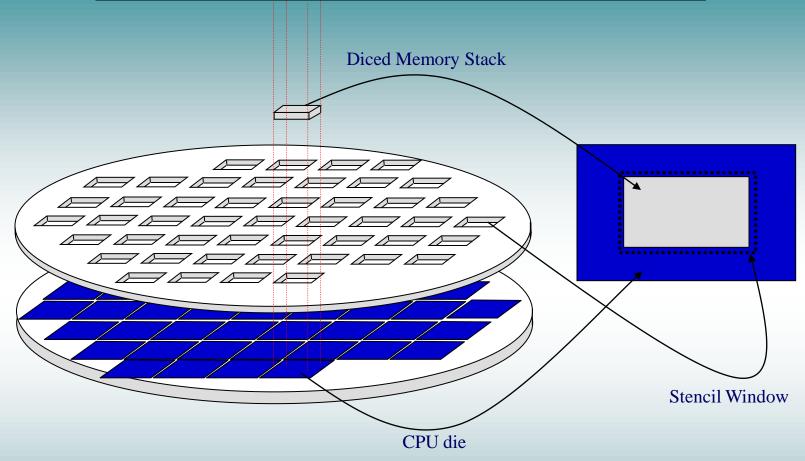

#### The "Killer" App: Split-Die

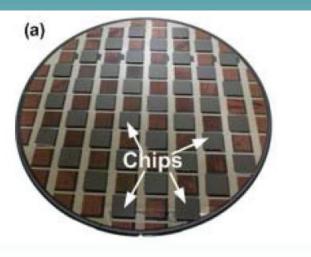

#### **Die to Wafer With Stencils**

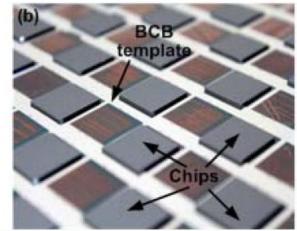

## **Die to Wafer With BCB Template**

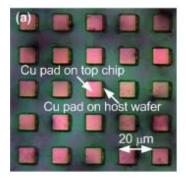

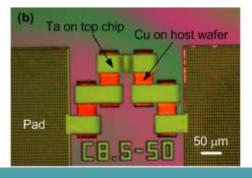

#### RPI Effort under Dr. James Lu

2um alignment / 5um pitch limit

Cu-Cu thermo compression bonding

Multilayer capability

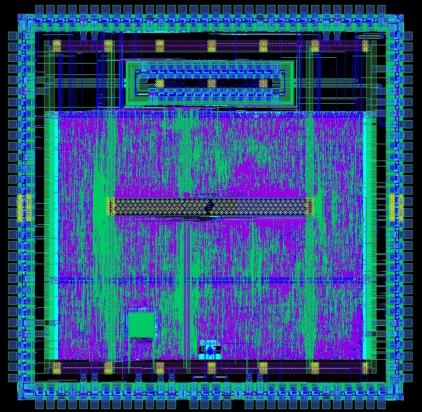

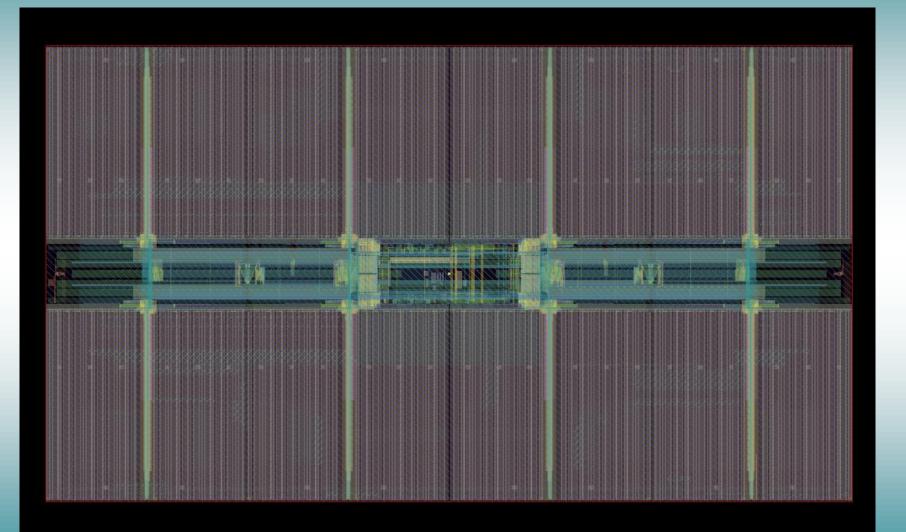

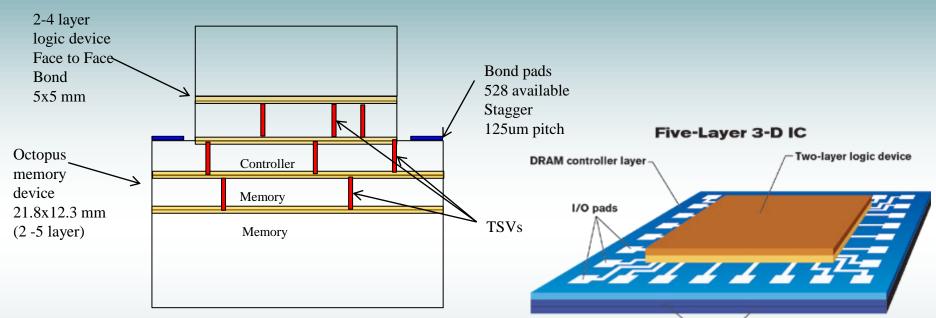

#### **Logic on Memory**

# **Hyper-Integration** 5-9 layer stacks

| Layer        | 5 Layer | 7 Layer | 9 Layer | Two layers of DRAM cells |

|--------------|---------|---------|---------|--------------------------|

| Poly         | 9       | 11      | 17      |                          |

| Copper Wire  | 21 (25) | 32 (38) | 34 (42) |                          |

| Al/W Wire    | 7       | 7       | 13      |                          |

| Trans. Count | 3B      | 3.1B    | 5.5B    |                          |

#### • Tools

- Partitioning tools

- 3D P&R

- Access

- Testing

- IEEE 1500

- IEEE 1149

- Standards

- Die level

- JEDEC JC-11 Wide bus memory

- Foundry interface

Tezzaron Semiconductor

05/05/2011

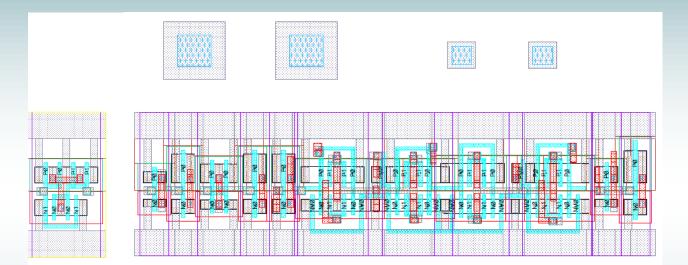

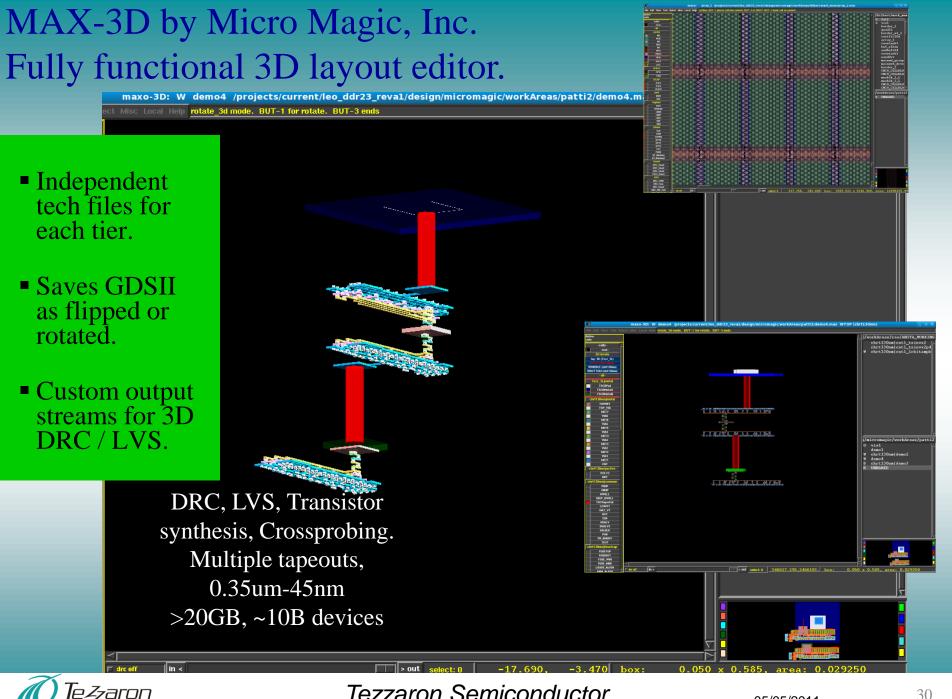

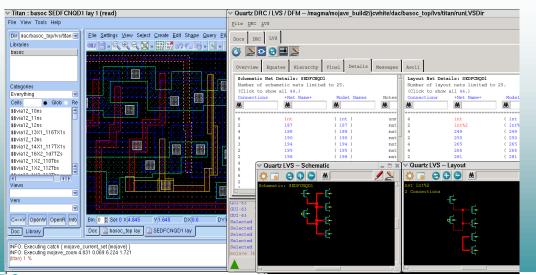

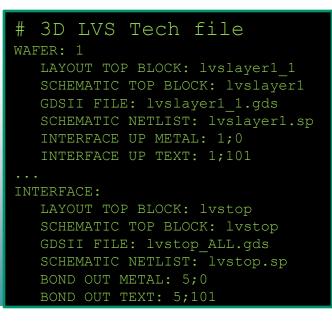

## **3D LVS using QuartzLVS from Magma**

- Key features

- LVS each of the 2D designs as well as the 3D interconnections between them in a single run

- Driven by a 3D "tech file" that specifies the number and order of layers, interconnect material, etc

- TSV aware LVS extraction

- Full debug environment to analyze any LVS mismatch

VUD

GND

suffer

GND

fiode array pr diode arra

Butte

Buffe

Tezzaron Semiconductor

31

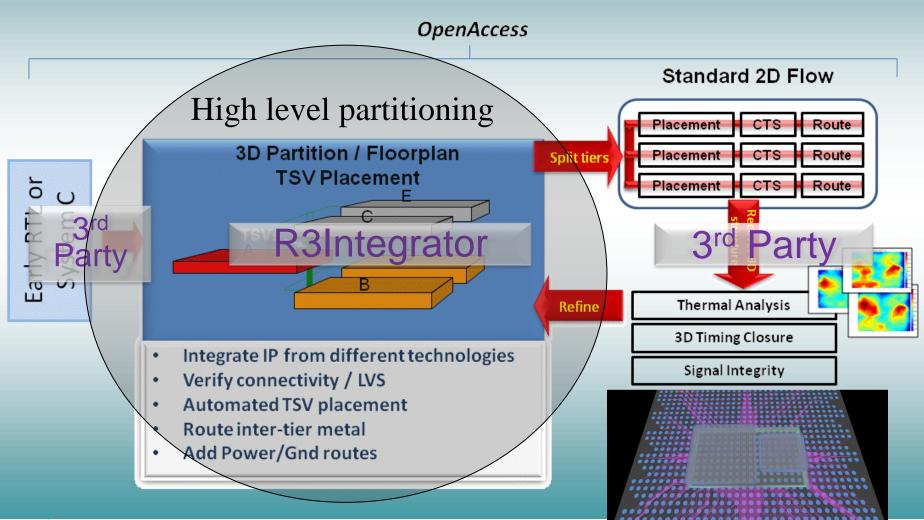

#### **R3Logic 3DIntegrator**

## **3D MPW**

- Complete 3D PDK 7<sup>th</sup> Release

- GF 130nm

- Calibre, Synopsis, Hspice, Cadence

- MicroMagic 3D physical editor

- Magma 3D DRC/LVS

- Artisan standard cell libraries

- Release 8 up coming

#### • MOSIS, CMP, and CMC MPW support

- July 1<sup>st</sup> MPW Tapeout

- 90nm, 150nm SOI

- Silicon Workbench

- >70 in process

- >400 users

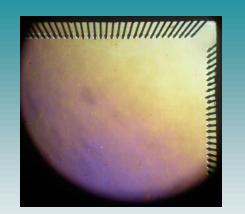

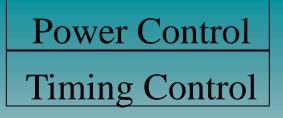

#### **Near End-of-Line**

How do we test this?

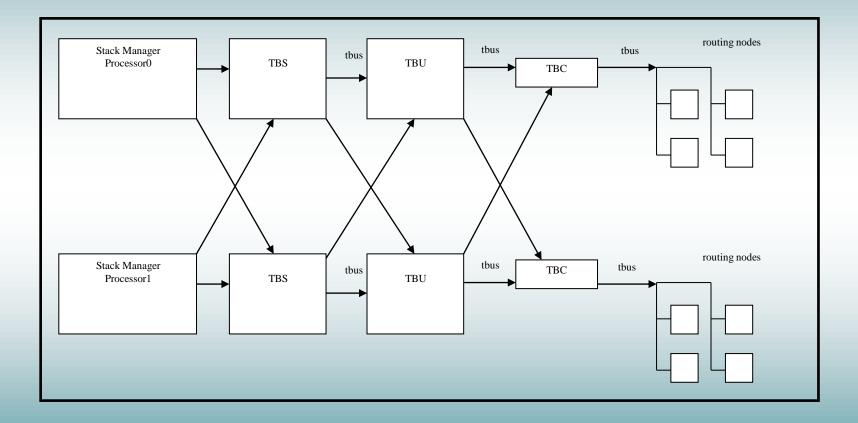

Test Engines (BIST, BISR) & NOCs

| Dual PPC 64x ARM SOC    |

|-------------------------|

| FPGA (CPU Augmentation) |

| DRAM                    |

| Flash                   |

| CAM                     |

| CAM                     |

| FPGA (Packet Cracker)   |

| Stack Controller        |

UC Event Detection

#### **Memory Test Processor**

- 1 inst/clk

- At speed testing

- Register file with inc/dec and compare

Row, Column, Layer

- Special complex instructions

- Activate, Test, Branch, Inc/Dec

- Data Scramble by Row, Column, Layer

- Restart instruction insertion

- Probe mode

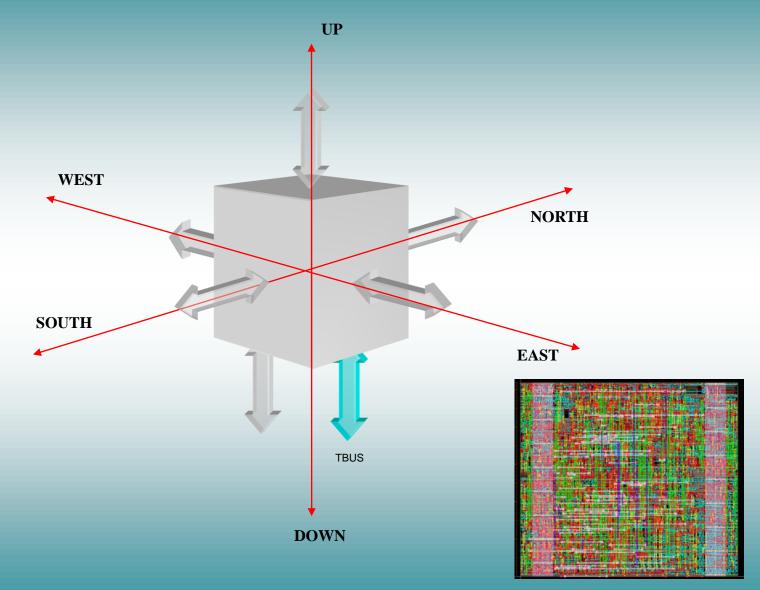

#### **Network-On-Chip: 3D-Routing Node**

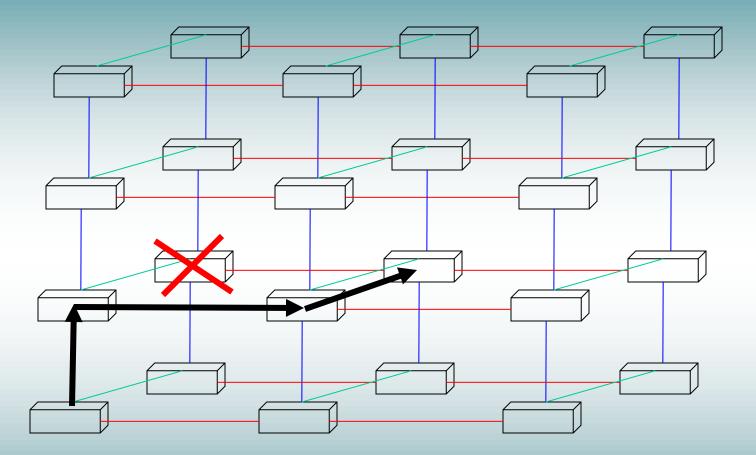

# **Fault Tolerant** Self-configuring/Re-configuring

#### **Summary**

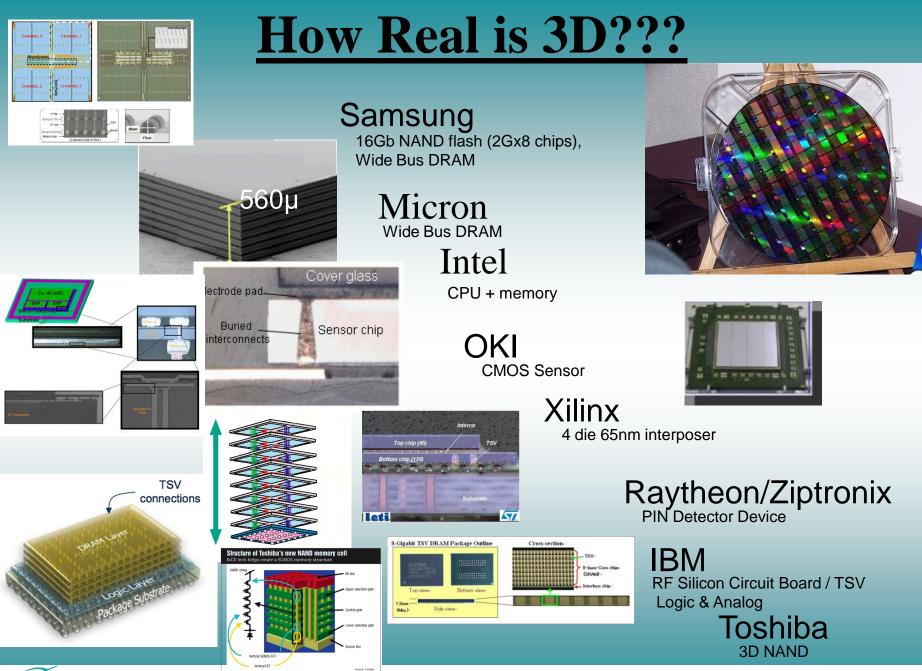

- 3D has numerous and vast opportunities!!

- New design approaches

- New ways of thinking

- New tools

- Poised for explosive growth

- 1-3 generation shrink equivalent

Sensors

Computing MEMS

Communications