### PAST

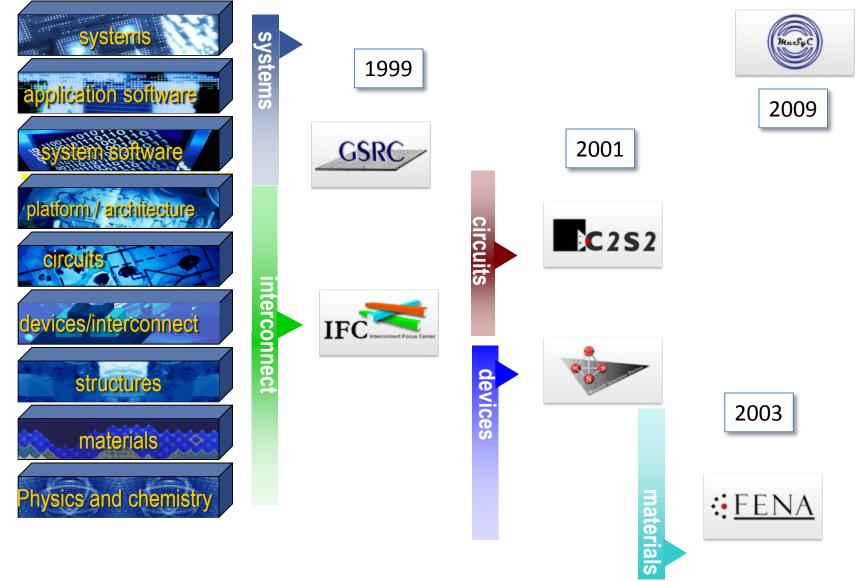

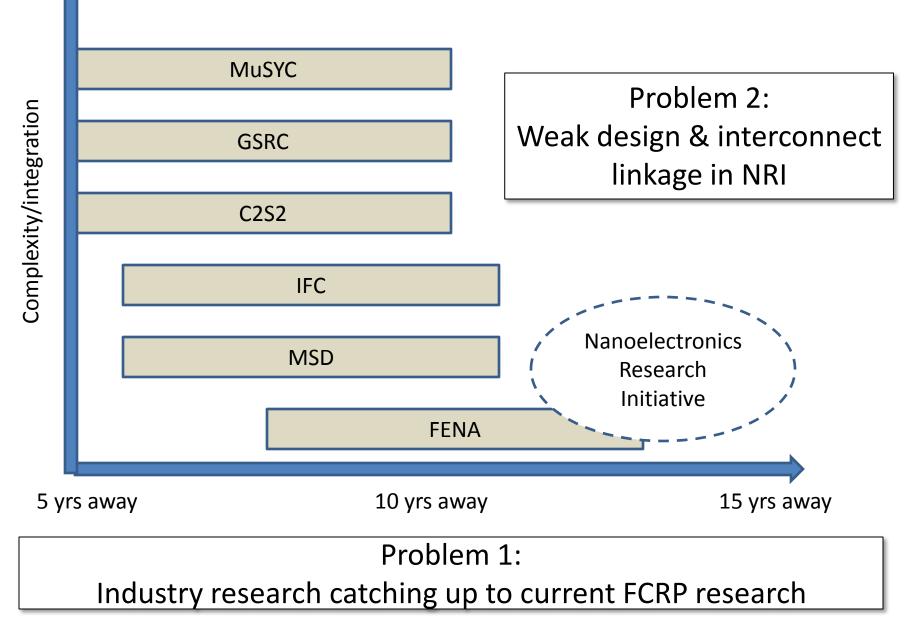

## **FCRP Center Evolution**

### PRESENT

### **Example Projects**

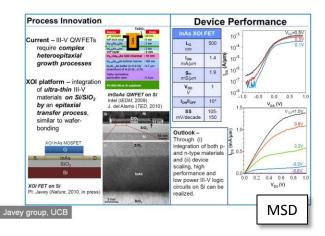

#### **Compound Semiconductor on Insulator (XOI)**

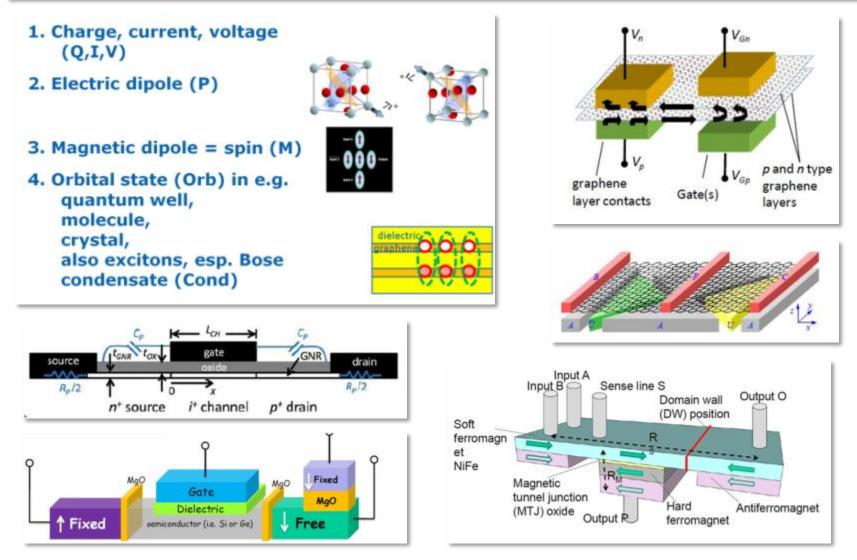

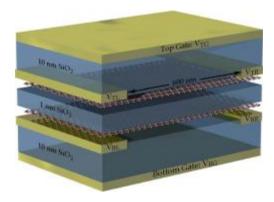

Use the unique electronic structure of graphene to demonstrate optics-like manipulation of electrons: focusing and reconfiguration

Use graphene as a reconfigurable wire in a CMOS circuit based on electron reflection at a p-n junction conductor

match model

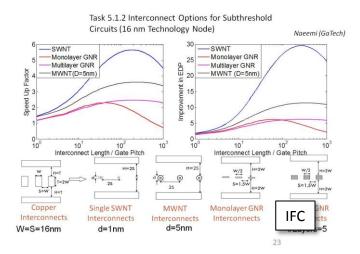

IFC & NRI

Source: FCRP Highlights, Nov 2010

## **Example Projects**

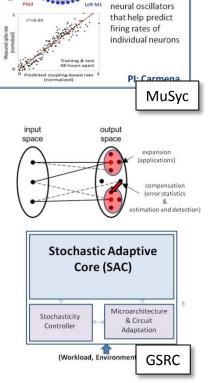

**Communication in Brain Networks**

Possible answer: Coordinated action

Result: Detected network of coupled

Unsolved problem: Network

coordination in brain

via neuronal oscillations

### NEMS/MEMS Relay Logic Circuits

- Circuits based on micro-mechanical "switcl controlled by electro-static voltages

- Adders, flip-flops, memories, DACs, ADCs have been fabricated and demonstrated

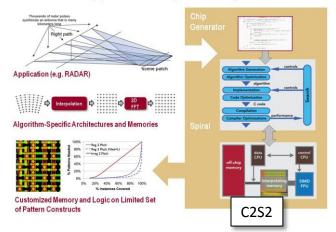

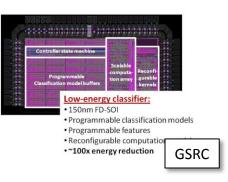

### Affordable Application-Specific Systems

Closed loop (*intelligent*) implantables: 10-100µW budget

Key Direction: Machine-learning based embedded/implanted devices

Source: FCRP Highlights, Nov 2010

### WE GAVE YOU WANT YOU ASKED FOR, WHAT'S THE ISSUE?

### YOU WILL MISS OPPORTUNITIES IF YOU ONLY LOOK FOR BETTER VERSIONS OF TODAY'S TECHNOLOGY AND PRODUCTS

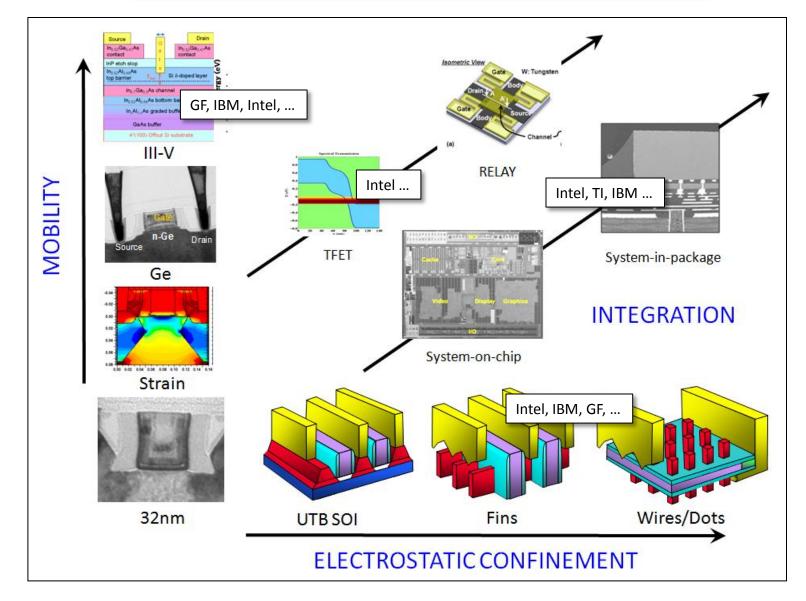

### Example: FCRP research becoming industry research

FCRP workshop – M Mayberry, May 2012

Source: Intel, Jan 2012

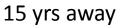

### **FUTURE**

## Push Further Out Recognize Inflection Points Coming

#### **NEXT: Systems Integration & Discovery**

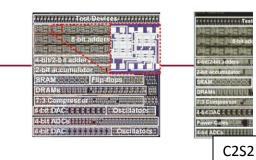

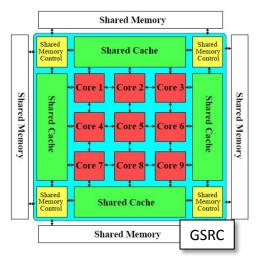

- Topics build off MuSyC/GSRC/C2S2

- Additional emphasis on design complexity, software, system-level verification and validation

- Integrates both CMOS & potentially beyond CMOS components

- Critical for systems in ~10 year range

furthe

out

Complexity/integration

## Planned Research Landscape

# NEXT – Highly Complex Systems

Mission: Enable highly complex systems with capabilities well beyond those available today, i.e., to augment beyond the "sum of the parts."

Focus on system – building blocks, methods, capabilities

- Zone 1: Complex heterogeneous networked systems

- Zone 2: Highly parallel centralized computation systems

### Technology Areas for NEXT –

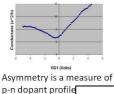

- High performance analog for high speed wireless; THz electronics for imaging, sensing, novel power devices

- Vehicle and Distributed Sensor Networks

- Computing System Architectures based on CMOS technology

- Tools and methods for design, verification, and predictive modeling, including physical modeling of thermal and structural impacts on functionality and the physics of failure of proposed components.

Opportunity to fund some emerging areas as special projects outside of main focus areas

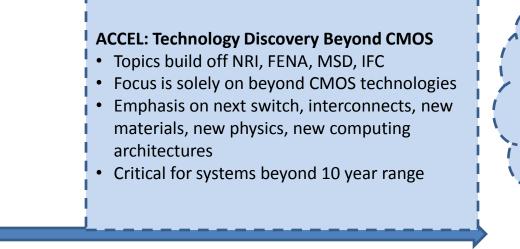

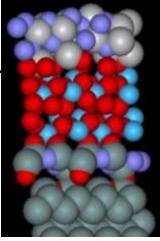

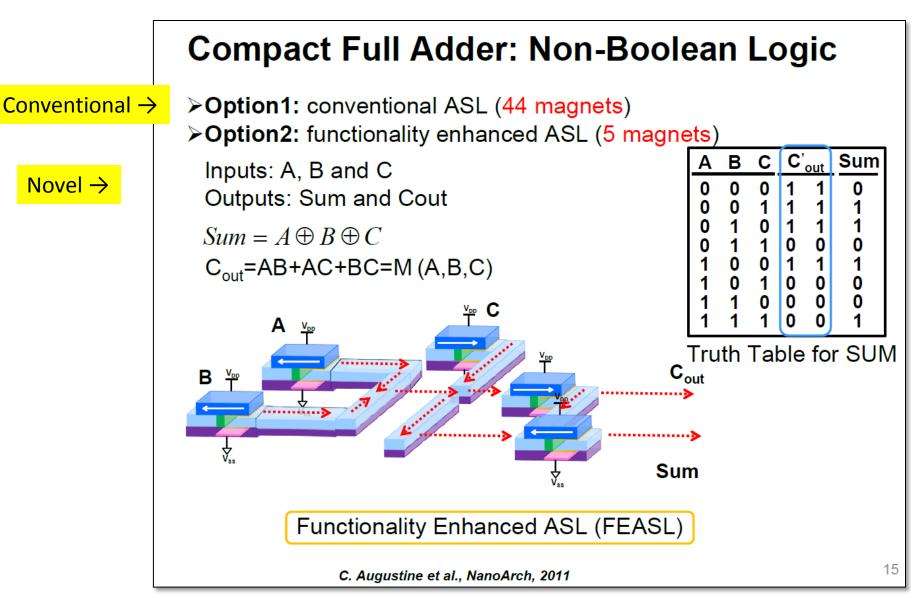

### ACCEL – Semiconductor Technologies Beyond CMOS

Mission: Identify and accelerate progress for new mainstream technologies beyond digital CMOS

- Focus areas structured with both focus on most promising concepts and continued seeding future technology ideas

- Necessary to look beyond simple replacements of existing digital CMOS elements, building blocks alone are not sufficient

- Anticipate and work at or beyond inflection points

### Technology areas for ACCEL –

- Nonconventional material systems

- Quantum engineered devices and new sensors and transducers

- Integrated circuits and computing architectures

Opportunity to fund some emerging areas as special projects outside of main focus areas

## **Example Inflection Points**

### End of Scaling is Near – Decades of predictions

"Optical lithography can't do sub-micron"

"Optical lithography will reach its limits in the range of 0.75-0.50 microns"

"Optical lithography should reach its limits in the 1990-1994 period"

"X-ray lithography will be needed below 1 micron"

"Minimum geometries will saturate in the range of 0.3 to 0.5 microns"

"Channel lengths can be reduced to approximately 0.2 micron"

"Channel lengths can be reduced to approximately 0.2 micron"

"Oxide reliability may limit oxide scaling to 2.2 nm"

"Plasma etched aluminum will not happen in our lifetime

"Copper interconnects will never work"

"Scaling will end in ~10 years"

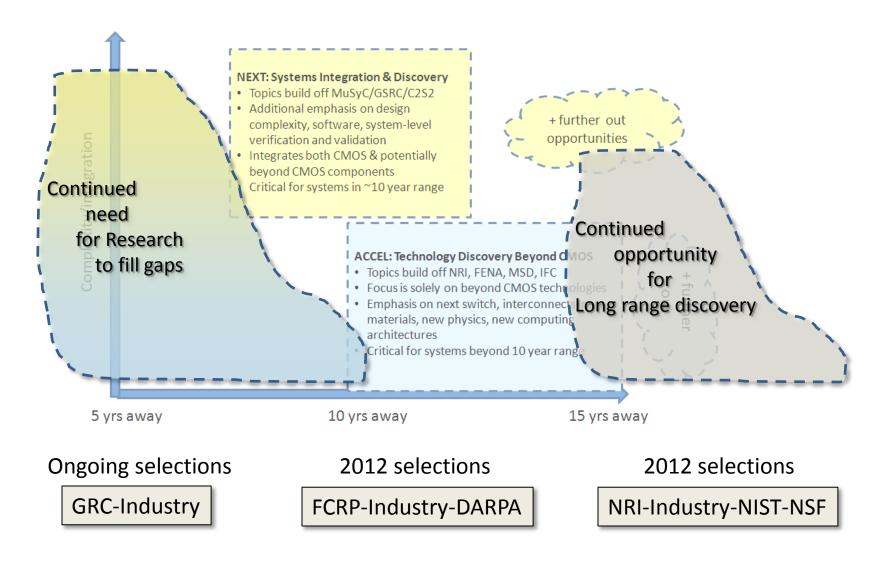

### **Inflection Points**

- Size Limited by Granularity, Process Control

- Size limited by Electrical behavior (tunneling)

- Voltage scaling limited by Mobility

- Interconnects limit Performance

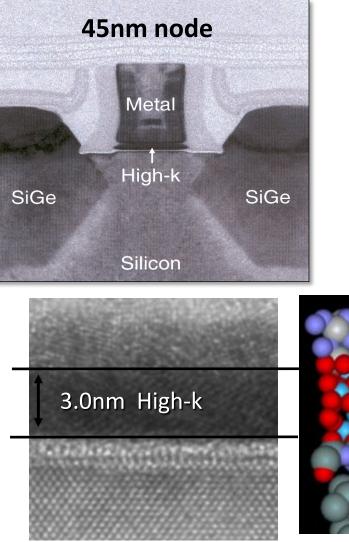

### Inflection Point: Granularity Limits Size Switch to Chemistry Driven Processes

3-4 atoms thick

Inflection Point: Size limited by Electrical behavior Switch to Different Device Operation Nanoelectronic Research Initiative – Search for Next Switch

### NRI: 18 New Devices Benchmarked as a Next Switch Most can be built with multiple active layers

| Code  | Device                     |  |  |

|-------|----------------------------|--|--|

|       | Units                      |  |  |

| REF-H | 15 nm CMOS                 |  |  |

| REF-L | 15 nm CMOS                 |  |  |

| -01   | Excitonic FET              |  |  |

| -04   | MTJ Logic Switch           |  |  |

| -05   | All Spin Logic             |  |  |

| -07   | Graphene PN Junction       |  |  |

| -08   | Electronic Ratchet         |  |  |

| VI-01 | Graphene thermal logic     |  |  |

| M-02  | BDD Architecture           |  |  |

| VI-04 | Nanomagnet logic           |  |  |

| M-05  | gnrTFET                    |  |  |

| M-06  | InAs TFET                  |  |  |

| V-02  | e-Struct. Modulation Trans |  |  |

| V-03  | RAMA                       |  |  |

| S-01  | BISFET                     |  |  |

| 5-02  | RIEFET                     |  |  |

| S-03  | HetTFET                    |  |  |

| N-02  | Spin Wave                  |  |  |

| N-04  | MTJ/STT                    |  |  |

| N-05  | Spin Torque Amplifiers     |  |  |

|       |                            |  |  |

# **Rethinking 3D**

| C | Driventional y                                 | Rethinking 3D                                            |                        |                                      |

|---|------------------------------------------------|----------------------------------------------------------|------------------------|--------------------------------------|

|   | Possible<br>Application                        | Bonding/ Fabrication Method                              | Connections            | Stacking<br>Objective                |

|   | Memory +<br>Logic                              | DRAM<br>SoC<br>PKG<br>PKG                                | ~1000s                 | Reduce<br>wiring/<br>form factor     |

|   | Multiple die<br>stacking                       | BF/ other ?<br>DRAM<br>SoC<br>PKG<br>Face to<br>back/DtD | ~1000s                 | Reduce<br>wiring/<br>form factor     |

|   | Smart unit<br>repartitioning<br>(logic+logic)  | Face to face/ WtW or DtD                                 | ~1M+                   | Reduce<br>wiring<br>(upper<br>layer) |

|   | Within unit<br>repartitioning<br>(logic+logic) | Face to face/<br>WtW or DtD                              | 1μm/0.5μm<br>~10M-100M | Reduce<br>wiring/<br>density?        |

| ♦ | Circuit /device<br>repartitioning              | Sequential processing                                    | 5-10nm<br>~10B+        | Density/<br>Disparate<br>Integration |

|   | Novel 7                                        | F                                                        | CRP workshop – M May   | /berry, May 2012                     |

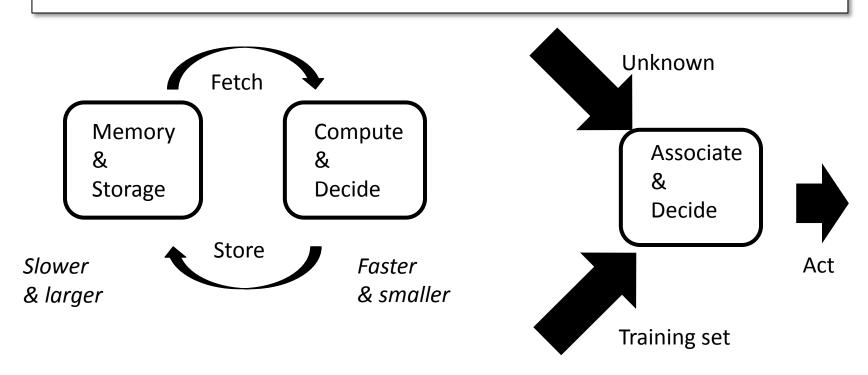

# **Rethinking Computation**

### **Exploring Other Ways to Compute**

"Von Neumann"

Bottleneck = memory/storage Transport limited devices make it worse

### Conventional

FCRP workshop – M Mayberry, May 2012

Bottleneck = training Potentially favorable for novel devices

### Interconnects are Pervasive

- New materials needed for novel interconnects

- Not sufficient to only explore device behavior

- Transducers to convert between domains

- Novel transport in highly interconnected 3D

- Working around transport limited computation

# Key Messages

- All Paths forward require Materials Research

- We need to rethink our approaches to both device & design technologies

- Systems can have unique abilities not planned at building block level. Use cross-functional approaches

- Interconnects and transport work differently for novel devices, how can we exploit that ?

- Optimal computation might be very different, where are the opportunities ?

- We want to identify & fund novel long term research, not just gaps that we can see

- Surprise us !