#### 5<sup>th</sup> Neuro-Inspired Computational Elements Workshop (NICE)

An Overview of Related NSF Programmatics

Erwin Gianchandani Deputy Assistant Director, NSF Computer and Information Science and Engineering

NSF

March 6, 2017

## **Future Computing**

"The end of dramatic exponential growth in single-processor performance marks the end of the dominance of the single microprocessor in computing. The era of sequential computing must give way to a new era in which parallelism is at the forefront."

#### 21<sup>st</sup> Century Computer Architecture

A community white paper May 25, 2012

| Late 20 <sup>th</sup> Century                                                                 | The New Reality                                                                                                                                    |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Moore's Law — 2× transistors/chip every 18-24 months                                          | Transistor count still 2× every 18-24 months,<br>but see below                                                                                     |

| Dennard Scaling — near-constant power/chip                                                    | Gone. Not viable for power/chip to double (with 2× transistors/chip growth)                                                                        |

| The modest levels of transistor unreliability easily hidden (e.g., via ECC)                   | Transistor reliability worsening, no longer easy to hide                                                                                           |

| Focus on computation over<br>communication                                                    | Restricted inter-chip, inter-device, inter-machine<br>communication (e.g. Rent's Rule, 3G, GigE);<br>communication more expensive than computation |

| One-time (non-recurring engineering) costs growing, but amortizable for mass-<br>market parts | Expensive to design, verify, fabricate, and test, especially for specialized-market platforms                                                      |

"Today, we stand at a point where exponential advances in the science and technology of computing and concomitant advances in approaches to brain sciences have ignited new opportunities to forge connections between these two fields."

#### Table 1: Technology's Challenges to Computer Architectur

#### A Federal Vision for Future Computing: A Nanotechnology-Inspired Grand Challenge

Collaborating Agencies: Department of Energy (DOE), National Science Foundation (NSF), Department of Defense (DOD), National Institute of Standards and Technology (NIST), Intelligence Community (IC)

#### Introduction

This white paper presents a collective vision from the collaborating Federal agencies of the emerging and innovative solutions needed to realize the Nanotechnology-Inspired Grand Challenge for Future Computing. It describes the technical priorities shared by multiple Federal agencies, highlights the challenges and opportunities associated with these priorities, and presents a guiding vision for the research and development needed to achieve key near-, mid-, and long-term technical goals. By coordinating and collaborating across multiple levels of government, industry, academia, and nonprofit organizations, the nanotechnology and computer science communities can look beyond the decades-old approach to computing based on the von Neumann architecture and chart a new path that will continue the rapid pace of innovation beyond the next decade.

#### Background

On October 20, 2015, the White House announced "A Nanotechnology-Inspired Grand Challenge" to develop transformational computing capabilities by combining innovations in multiple scientific disciplines. The Grand Challenge addresses three Administration priorities—the National Nanotechnology Initiative (NNI),<sup>1</sup> the National Strategic Computing Initiative (NSCI),<sup>2</sup> and the Brain Research through Advancing Innovative Neurotechnologies (BRAIN) Initiative<sup>3</sup> to:

Create a new type of computer that can proactively interpret and learn from data, solve unfamiliar problems using what it has learned, and operate with the energy efficiency of the human brain.<sup>4</sup>

While it continues to be a national priority to advance conventional digital computing—which has been the engine of the information technology revolution—current technology falls far short of the human brain in terms of the brain's sensing and problem-solving abilities and its low power consumption. Many experts predict that fundamental physical limitations will prevent transistor technology from ever matching these characteristics.

#### Call for a Coordinated Approach

In the announcement, the White House challenged the nanotechnology and computer science communities to look beyond the decades-old approach to computing based on the von Neumann architecture and chart a new path that will continue the rapid pace of innovation in information technology beyond the next decade. There are growing problems facing the Nation that the new computing capabilities envisioned in this challenge might address, from delivering individualized

# FOR A GRAND CHALLENGE

White paper released by DOE, NSF, DOD, NIST, IC July 29, 2016

<sup>&</sup>lt;sup>1</sup> http://www.nano.gov

<sup>&</sup>lt;sup>2</sup> https://www.whitehouse.gov/blog/2015/07/29/advancing-us-leadership-high-performance-computing

<sup>&</sup>lt;sup>1</sup> https://www.whitehouse.gov/BRAIN

http://www.nano.gov/futurecomputing

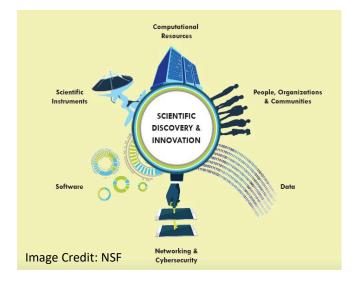

## **CISE programs address national priorities**

**Big Data**

Cybersecurity

National Robotics Initiative

#### Understanding the Brain

National Strategic Computing Initiative

Smart Cities

Computer Science for All

Advanced Wireless Research

For a comprehensive list of CISE funding opportunities, visit: <u>http://www.nsf.gov/funding/pgm\_list.jsp?org=CISE</u>

# **Understanding the Brain (UtB)**

- Enables scientific understanding of the full complexity of the brain, in action and in context, through targeted, cross-disciplinary investments

- CISE programs:

- Collaborative Research in Computational Neuroscience (CRCNS) in collaboration with NIH, Germany, France, and Israel

- Integrative Strategies for Understanding Neural and Cognitive Systems (NSF-NCS) with EHR, ENG, and SBE

- CISE/IIS Robust Intelligence core program

- Science & Technology Center for Brains, Minds, and Machines

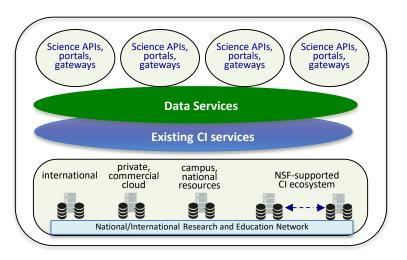

# National Strategic Computing Initiative (NSCI)

- NSF investments in NSCI aim to:

- Increase coherence between technology used for modeling and simulation and that used for data analytics

- Establish a path forward for future HPC systems after reaching the current limits of semiconductor technology (in the "post Moore's Law era")

- Advance scientific discovery through the broader High-Performance Computing (HPC) ecosystem

- NSF co-leading with DOD and DOE

## Scalable Parallelism in the Extreme (SPX)

Increasing computing performance in the modern era of parallel computing

- Aligns with NSCI

- Aims to establish collaborations among researchers representing all areas from the application layer down to the microarchitecture

- Proposals required to have two or more PIs providing different, distinct expertise

- Research areas:

- Algorithms

- Programming Languages and Systems

- Applications

- Architecture and Systems

- Extensible Distributed Systems

- Performance Predictability

- \$60M invested in FY 2013-FY 2016 under XPS; new competition in FY 2017

### **Energy-Efficient Computing: From Devices to Architectures (E2CDA)**

- Challenge: Future performance improvements across the board are now severely limited by the amount of energy it takes to manipulate, store, and critically, transport data

- Aligns with NSCI and nanotechnology-inspired Grand Challenge for Future Computing:

- Disruptive system architectures, circuit microarchitectures, and attendant device and interconnect technology aimed at achieving the highest level of computational energy efficiency

- Revolutionary device concepts and associated circuits and architectures that will greatly extend the practical engineering limits of energy-efficient computation

- Funded \$18M in new awards in FY 2016; new competition in FY 2017

#### NSF/Intel Partnership on Computer Assisted Programming for Heterogeneous Architectures (CAPA)

- Aims to significantly improve software development productivity by partially or fully automating software development tasks

- Proposals should address Programmer Effectiveness, Performance Portability, and Performance Predictability within the research areas:

- Programming abstractions and methodologies

- Program synthesis and learning

- Hardware-based abstractions

- Software engineering tools and practices

- Intel agreements contain provisions for possible direct, on-site participation in research by Intel researchers-in-residence

### **Future Computing**

- Tremendous national need and opportunity

- Long-term focus and approach

- Cross-agency and cross-section collaborations essential