# From Failure to Success:

# High-risk Semiconductor Research – A Lesson in Serendipity

Suman Datta

Stinson Professor, University of Notre Dame

Former and current students

Doyle, Kavalieros, Doczy, Metz, Dewey, Chau (Intel)

Engel-Herbert, Mayer, Narayanan (Penn State)

Salahuddin (Berkeley), Schlom (Cornell), Kummel (UCSD),

Raychowdhury, Khan, Naemi, Yu (GTech), Pop ( Stanford),

Ye, Roy (Purdue), Cho (UTDallas), Fay, Niemier, Hu (Notre Dame)

# My journey

- Learn from doing things (corporate research)

- Inspire the students (academic career)

- Lead a multi-university center (my current life)

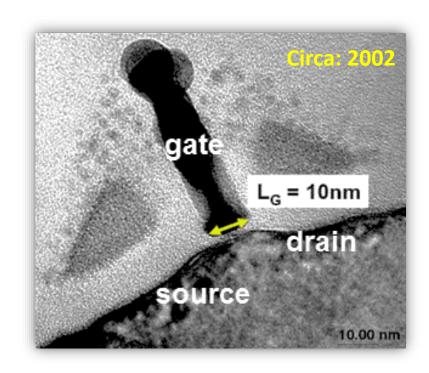

### 10nm Transistor

B. Doyle, S. Datta, J. Kavalieros, R. Chau, "Transistor Elements for 30nm Physical Gate Lengths and Beyond" Intel Technology Journal, May 2002

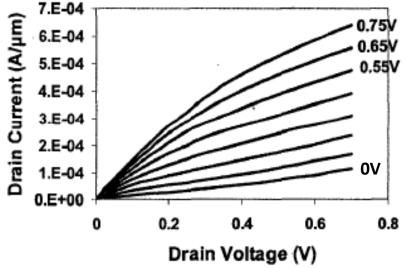

Figure 8: Family of Id-Vd curves for the 10nm research device.

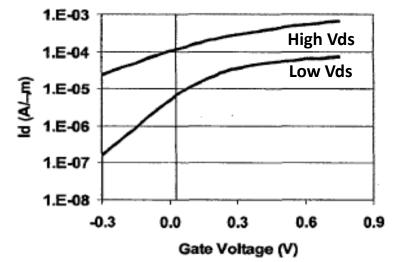

Figure 7: Id-Vg characteristics at Vd=50mV and 0.75V for the 10nm experimental device.

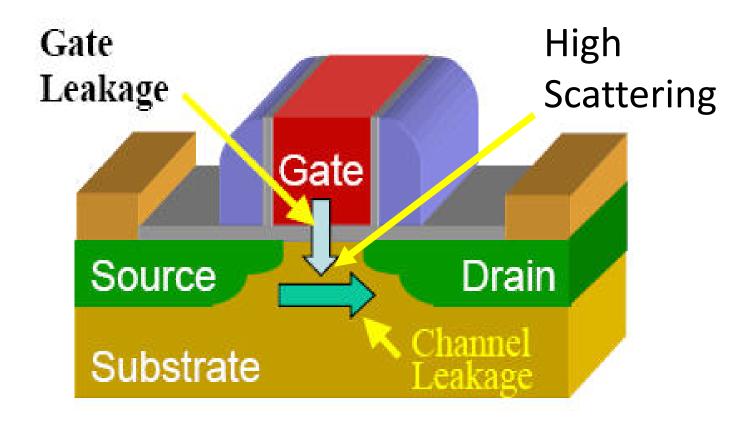

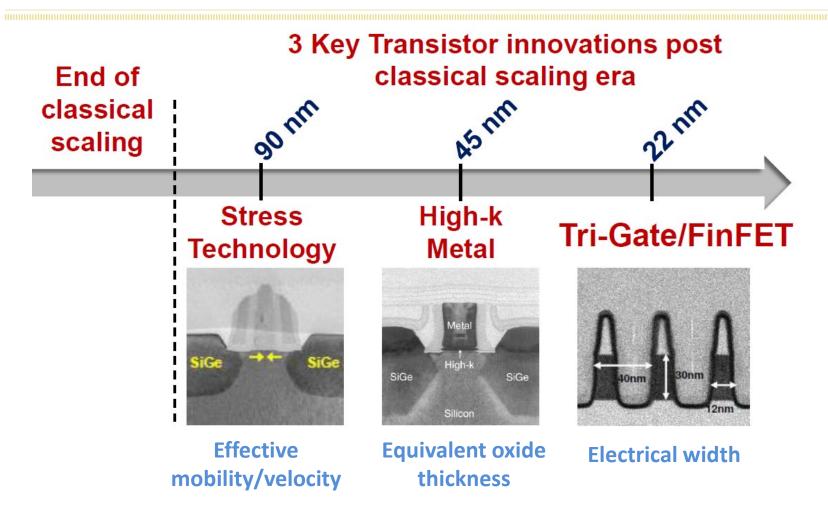

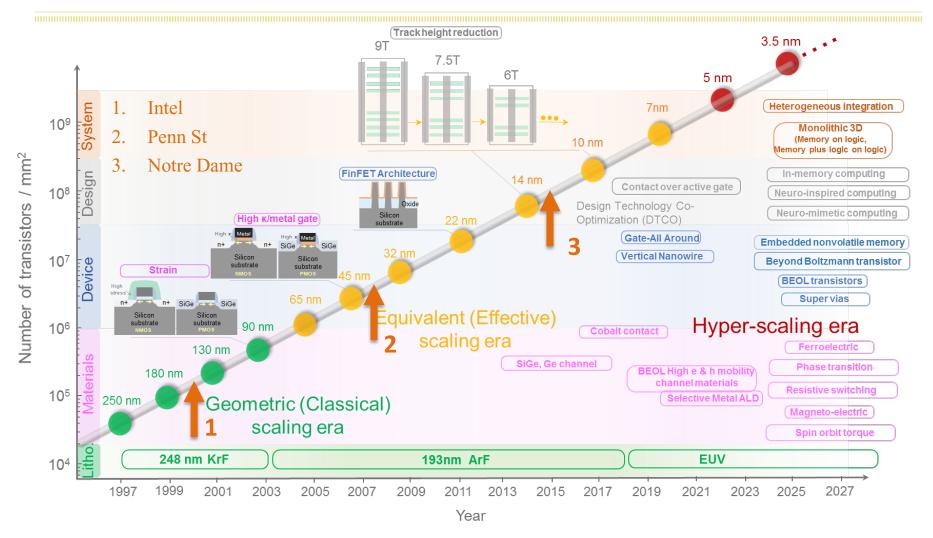

## Classical Scaling Ends

Need fundamental innovations to a) improve channel transport, b) reduce gate leakage and c) improve electrostatics

# **Equivalent Scaling Begins**

3 key transistor innovations that shaped this era of effective scaling Lessons in serendipity embedded in each

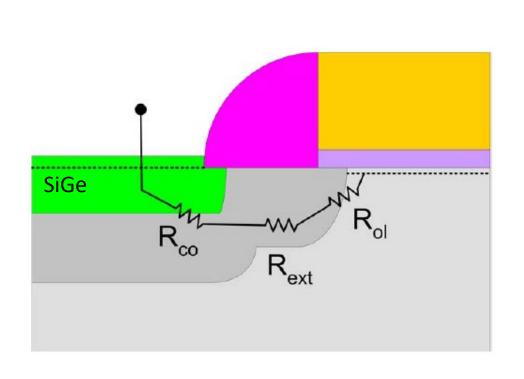

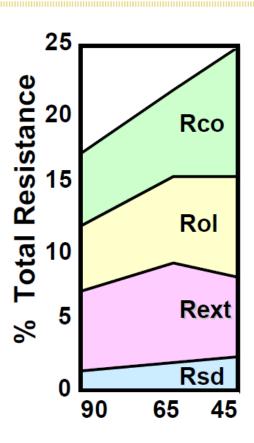

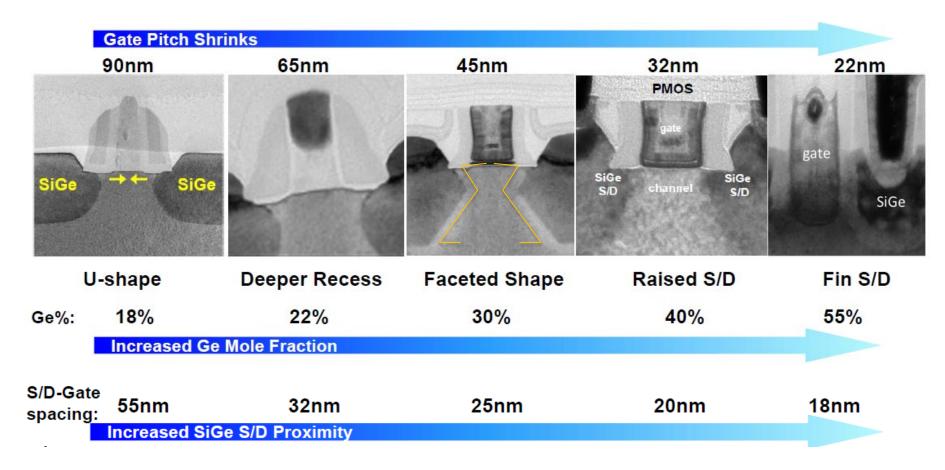

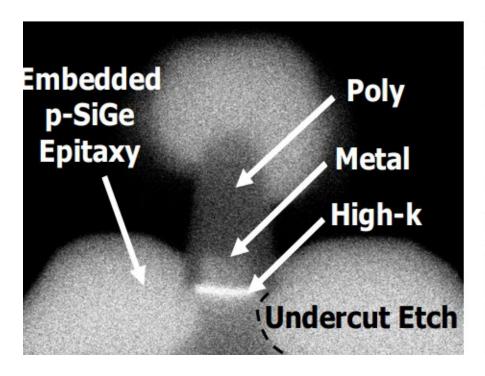

### **Elevated Source Drain**

Series resistance gets bigger fraction of on-resistance

### **Embedded Source Drain**

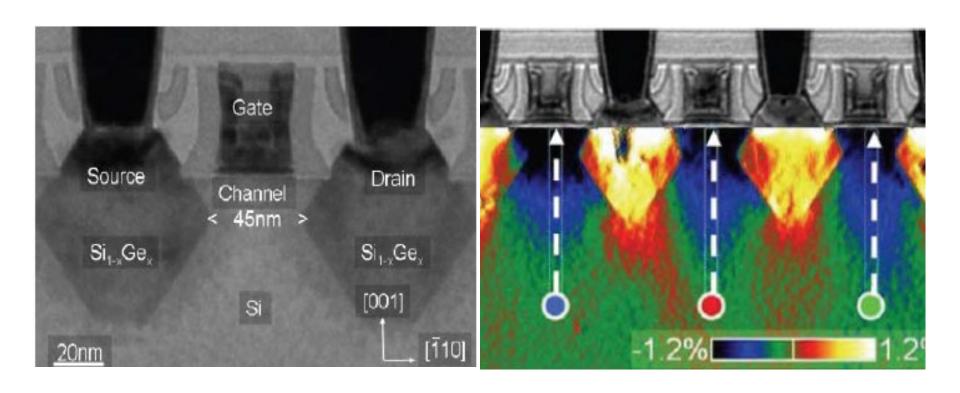

Hole mobility responds in a remarkable fashion Local stressor in PMOS and does not affect NMOS

### **Local Stressor**

SiGe S/D was intended for lowering external resistance eSiGe S/D becomes a local stressor for the channel

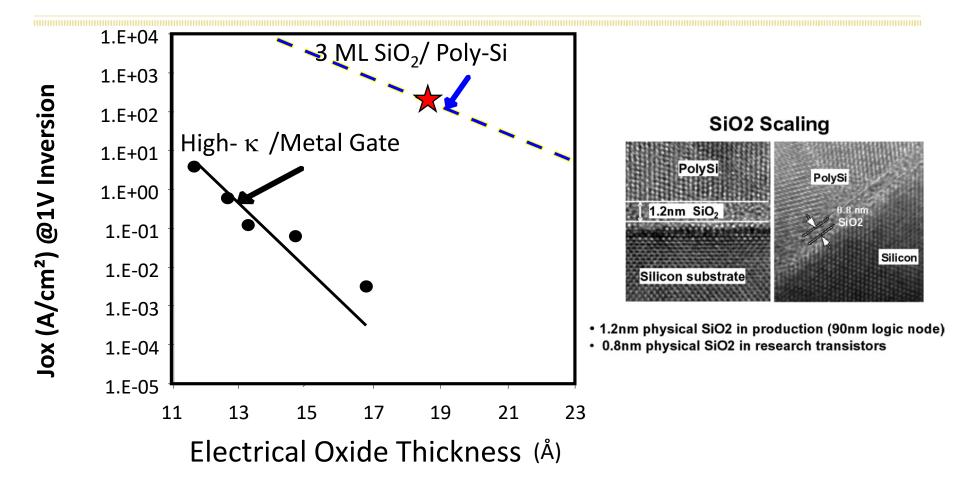

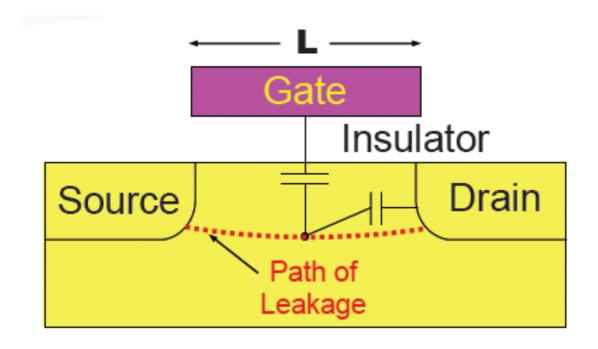

# High-k metal-gate

Gate leakage increases with  $SiO_2$  scaling -> running out of atoms High-k (HfO<sub>2</sub>) Gate Stack enables  $T_{elec}$  scaling with low gate leakage

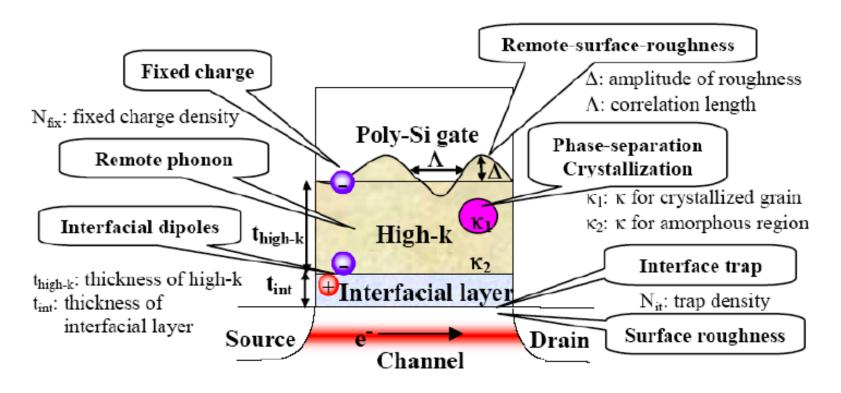

# **Gate Stack Challenges**

S. Saito, et al., IEEE IEDM, Washington, DC, Dec., 2003.

Bulk & interface traps: Poor reliability

Remote phonon scattering: Poor mobility

Technology Integration: Complexity and cost

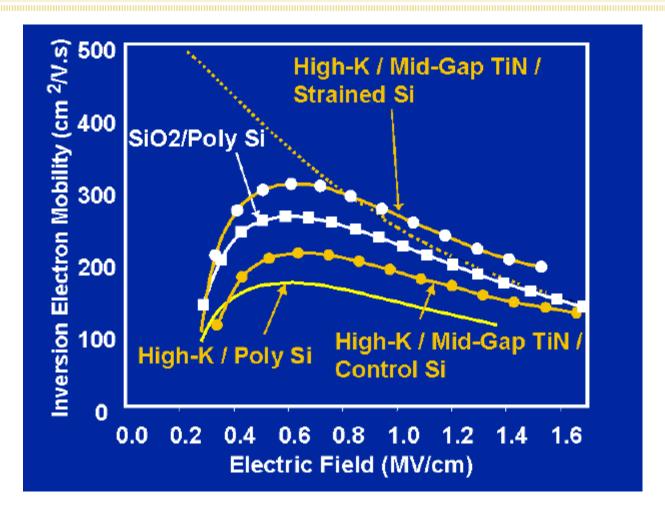

# Strained Si + High-k / MG stack

Combined channel strain + high-k + metal gate to recover mobility

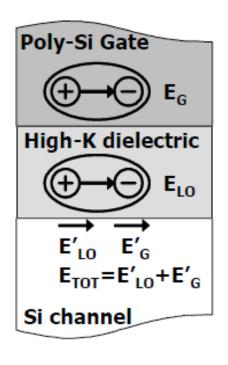

## Metal Gate Screening

(a) In resonance

(b) Off resonance

poly-Si gate plasmon frequency in resonance with HfO<sub>2</sub> dipoles degrading channel mobility

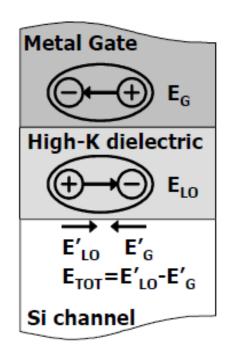

### Gate-Last Enhances Channel Strain

Gate last was intended for gate metal WF engineering Longitudinal compressive strain  $\epsilon_{xx}$  is enhanced Replacement metal gate acts as effective stress enhancers

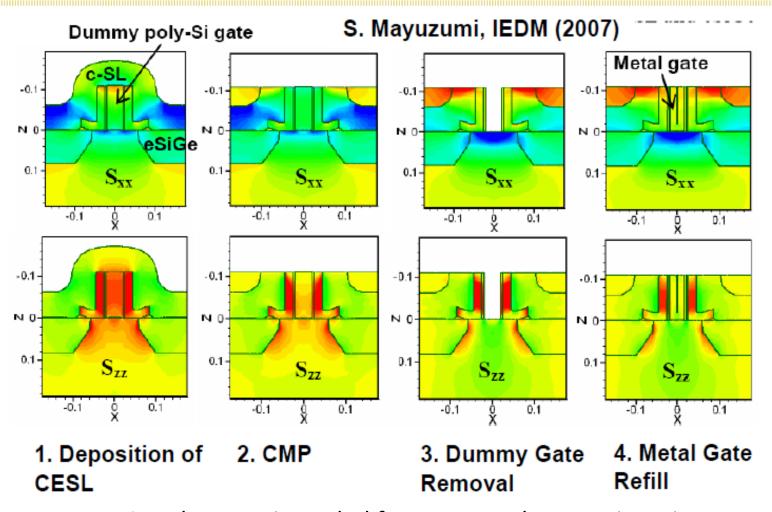

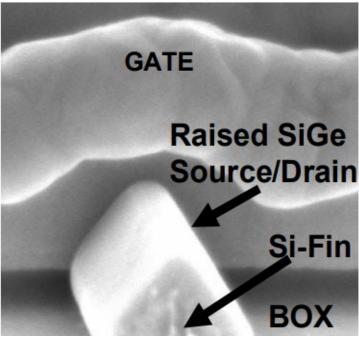

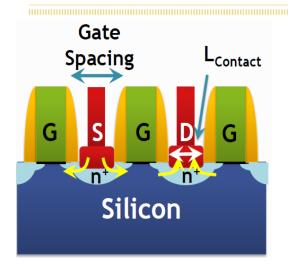

### Multi-Gate Transistor

"Even thin insulators cannot control leakage paths that are away from the gate"

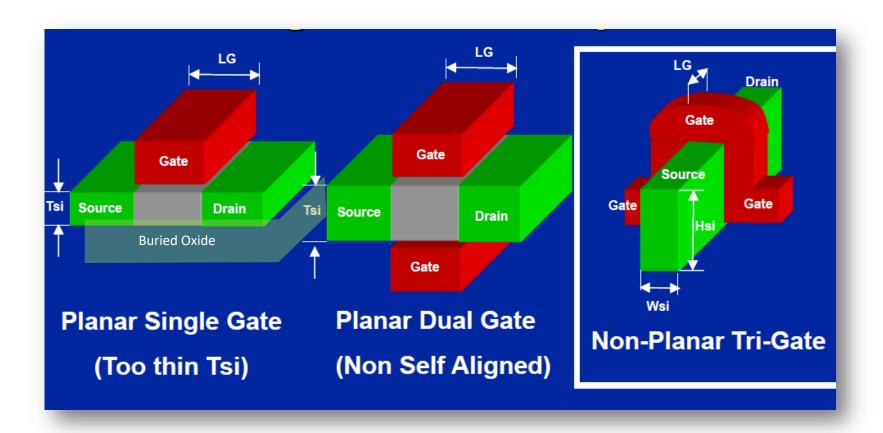

# From Single-Gate to Tri-Gate

Ultra thin body, double-gate or Tri-Gate architecture allows gate length scaling

### High Performance Tri-gate transistors

Combine the benefits of fully depleted Tri-gate architecture with high-k /metal gate stack, strain and crystallographic plane engineering

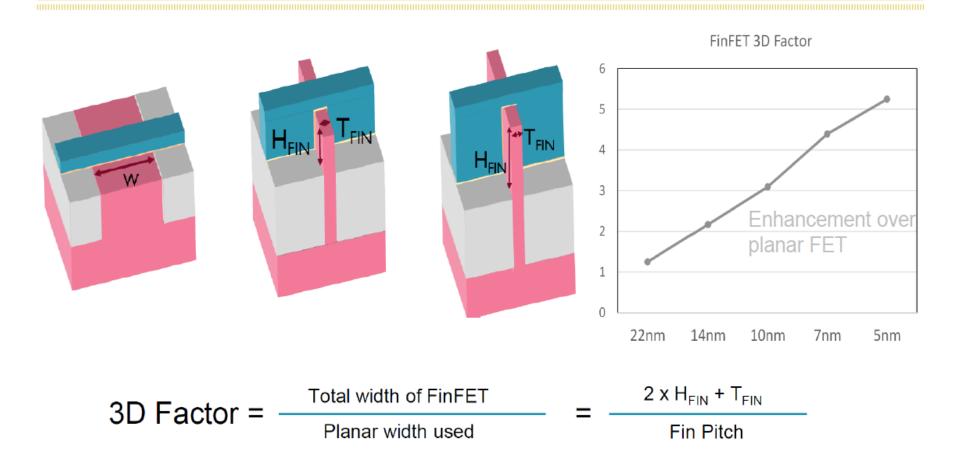

# **Electrical Width**

Part of Tri-gate appeal is improved electrostatics Other part is **folded width**

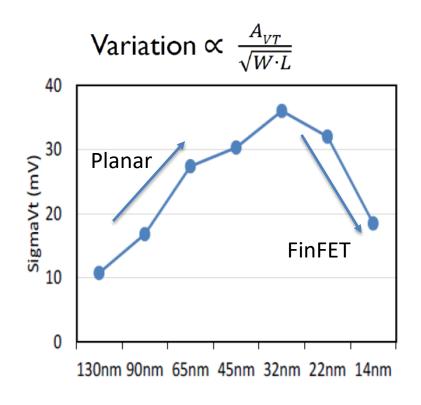

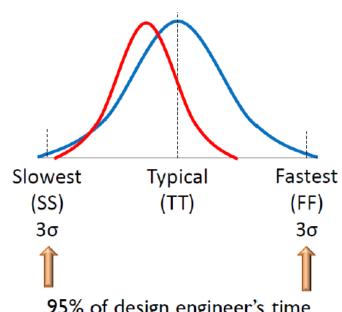

# Improved Variation

95% of design engineer's time

S. Natarajan (Intel), IEDM 2014

Greg Yeric (ARM), IEDM 2015

Tri-gate was intended primarily for electrostatics FinFET 3D factor enabled effective width scaling with improved variation

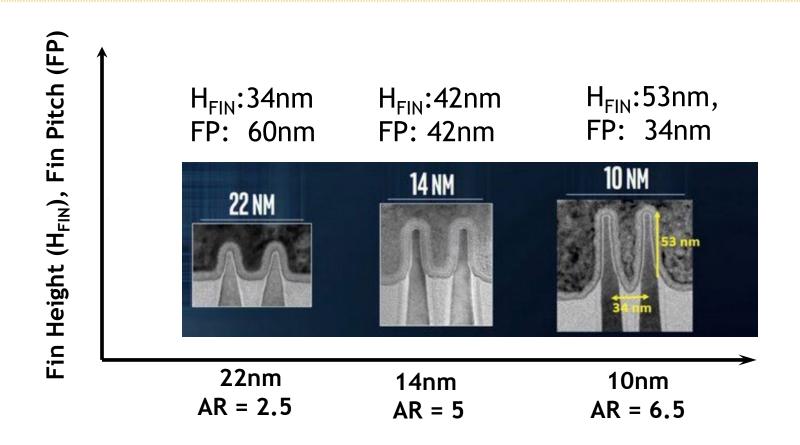

## FinFET evolution

Fin height and fin pitch evolution over last 3 generations

# Academic Career Begins ....

# PENN NEWS

HOME RESEARCH ACADEMICS IMPACT CAMPUS LIFE ATHLETICS ADMINISTRATION ARTS AND ENTERTAINMENT

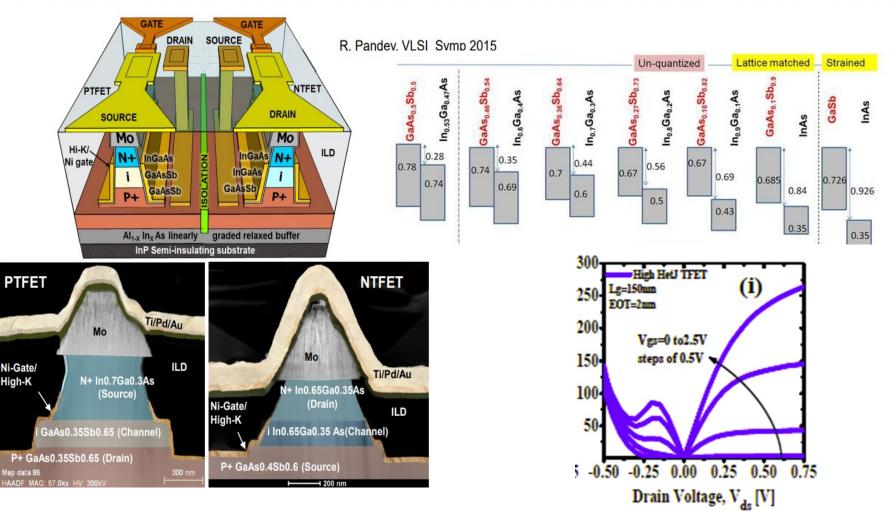

From left, Suman Datta, professor of electrical engineering at Penn State, and doctoral student Dheeraj Mohata, in the University's Nanoscale Devices at Circuits Lab. On the screen behind them is a model of their heterojunction tunneling field effect transistor (TFET).

IMAGE: Penn State

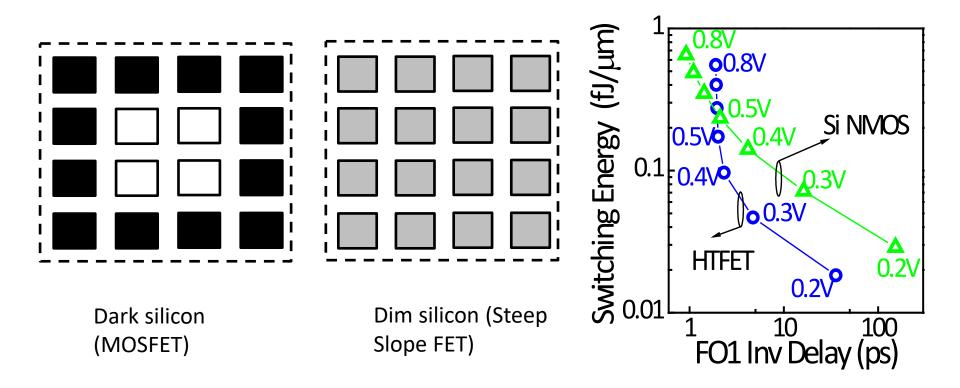

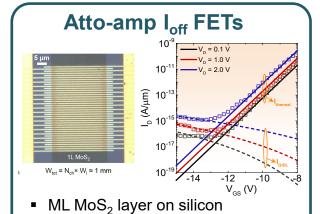

# Steep Slope FETs: Dark to Dim Silicon

Steep slope  $(\langle kT/q \rangle)$  transistors to operate with higher performance than MOSFETs at lower supply voltages

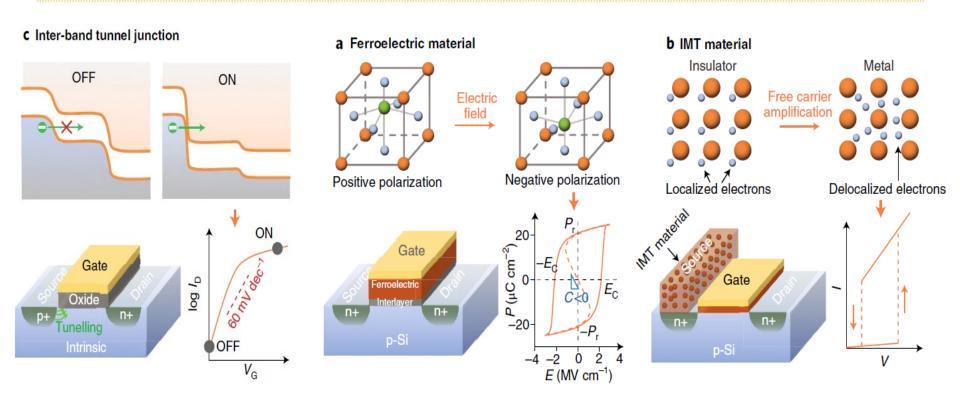

# Steep slope FETs

Inter-band tunneling, Ferroelectric negative capacitance, Insulator-metal phase transitions to enable transistors with *steep slope and low voltage operation*

# Heterojunction Tunnel FETs

Tunnel FETs can beat sub-threshold CMOS

Risk: On-current limitation to support high-performance computing

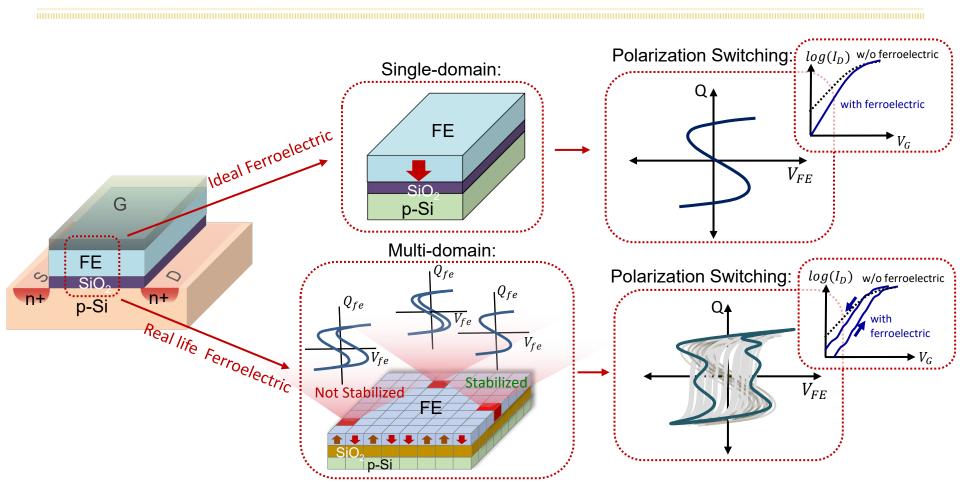

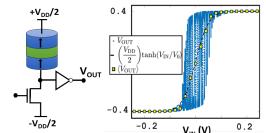

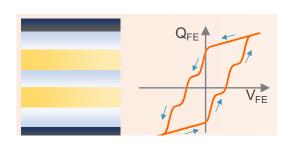

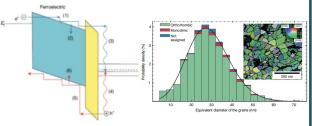

### Ferroelectric NCFETs

NCFETs can beat super-threshold CMOS

Risk: Stabilization of negative capacitance in multi-domain Ferroelectric

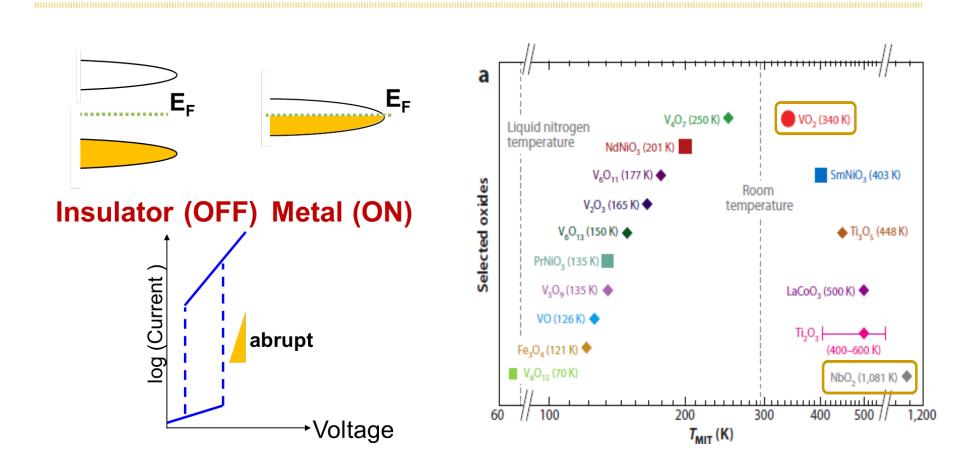

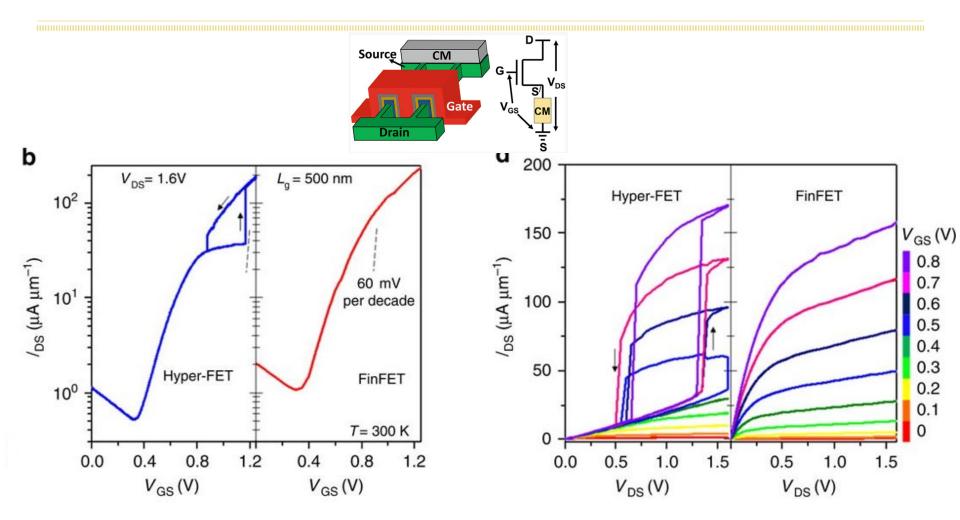

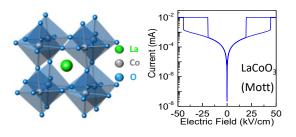

### Phase Transition in Correlated Oxides

Electrically induced collapse of transport gap around the Fermi level

# Phase Transition FETs

Phase Transition FETs show on-off ratio gain over traditional FETs Risk: phase transition is triggered at high current level in nanosec time scale

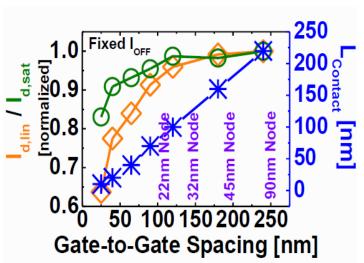

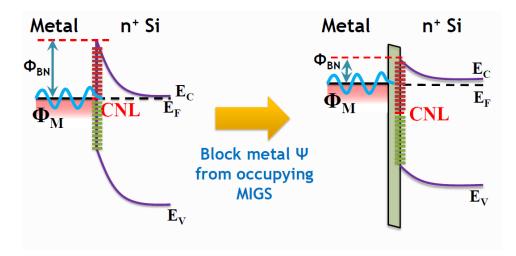

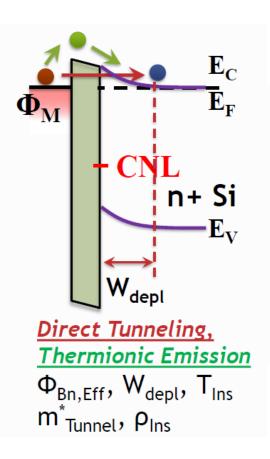

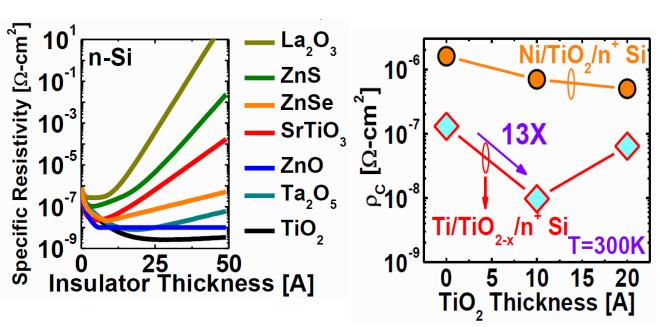

### **Tunnel FET to MIS Tunnel Contact**

$$\rho_c \propto \exp\left(\frac{\Phi_{BN}}{\sqrt{N_D}}\right)$$

Fermi level pinning prevents barrier height reduction

Insert an insulator between metal and silicon

### **MIS Tunnel Contact**

•  $\rho_C = 9.1 \times 10^{-9} \,\Omega$ -cm<sup>2</sup> obtained using M-I-S contact

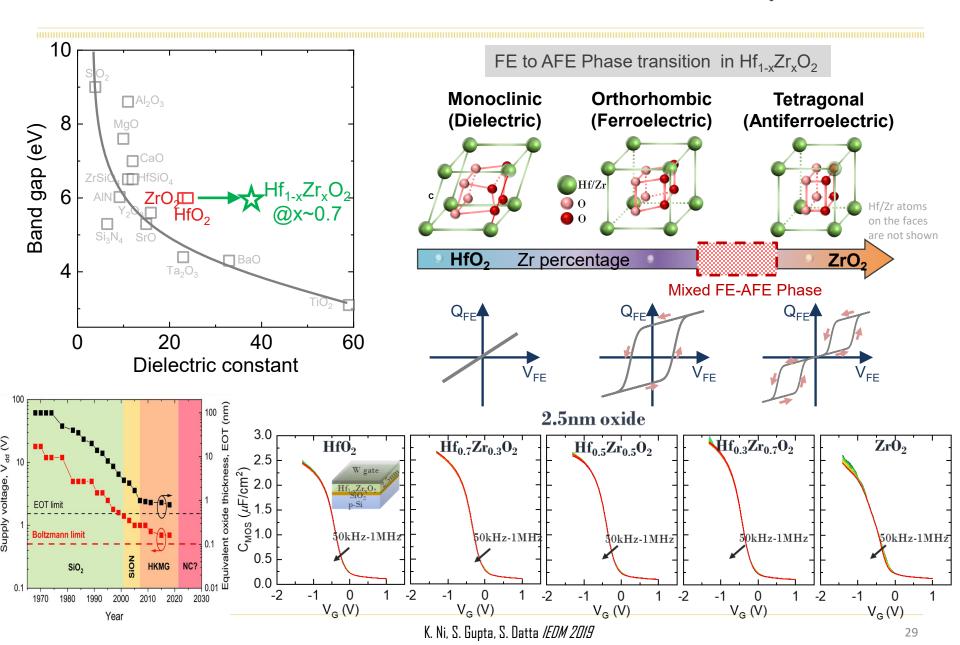

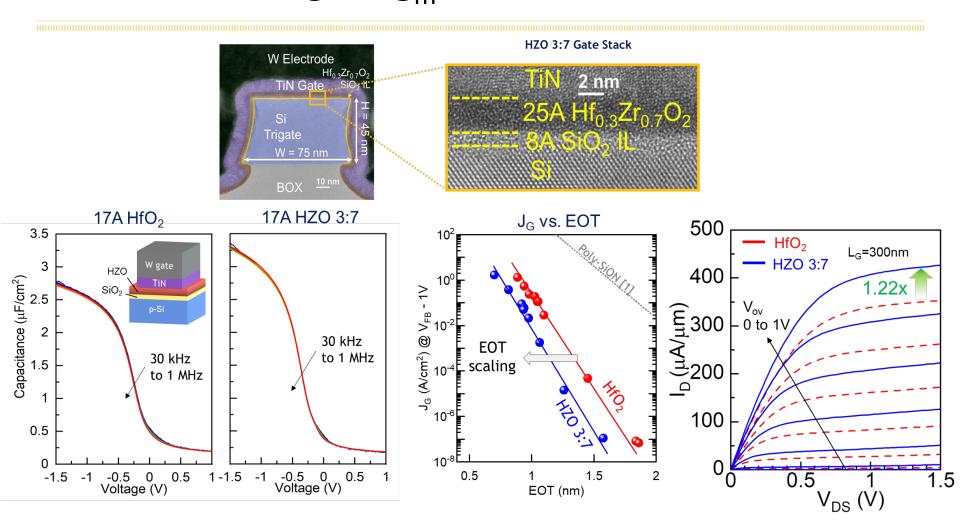

### NCFET to Low EOT MOSFET

# Thinner EOT, higher g<sub>m</sub> MOSFET

22% EOT scaling without mobility degradation was demonstrated in Tri-gate FETs with mixed FE-AFE phase higher- $\kappa$  dielectric (70% Zr-doped HfO<sub>2</sub>) gate-stack

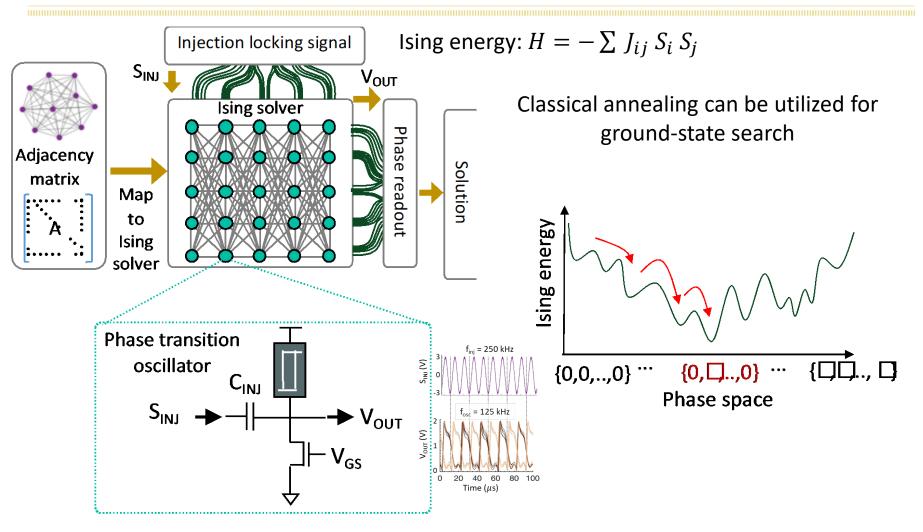

# Phase FET to Phase Transition Nano Oscillator WNOTRE DAME

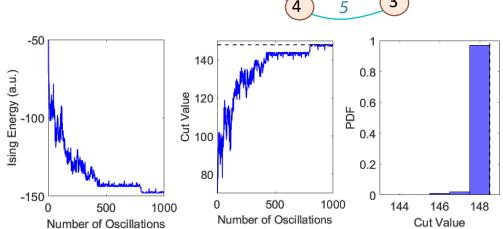

Harness continuous-time dynamics of a network of coupled phase transition oscillators to construct an electronic *Ising Hamiltonian solver operating at room temperature*

# Phase FET to Phase Transition Nano Oscillator WNOTRE DAME

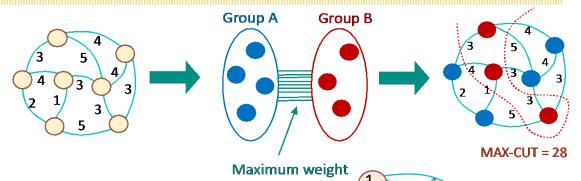

### **MAX-CUT Problem:**

Partition graph to maximize weights of edges crossing the cut

### Map MAX-CUT to Ising Model

- Represent nodes as spins  $s_i$

- Represent edges as "antiferromagnetic" coupling

- Minimizing Ising energy

$$H = -\sum_{i < j} W_{ij} s_i s_j$$

Use coupled oscillator network to efficiently solve Max-Cut Problem

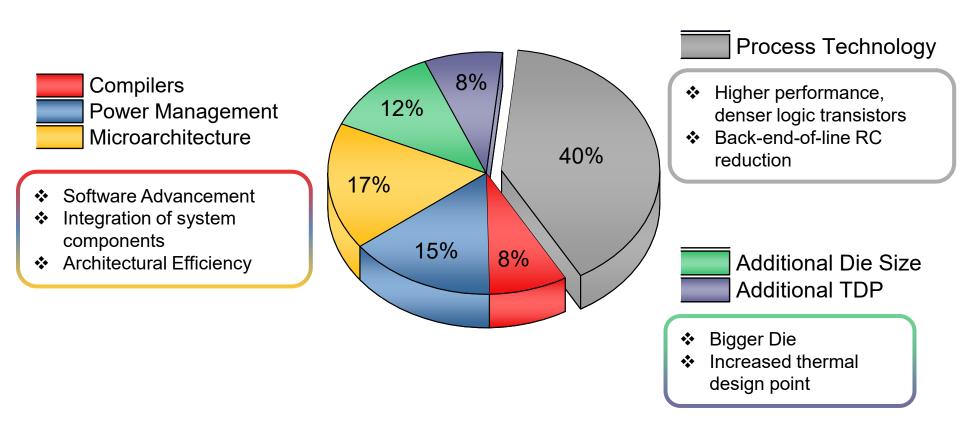

### **Transistor Scaling slowing down?**

Need a holistic approach to semiconductor research

### **Compute Performance Gain**

60% of compute performance gain over last decade came from advances in process technology, die size increase and thermal design point

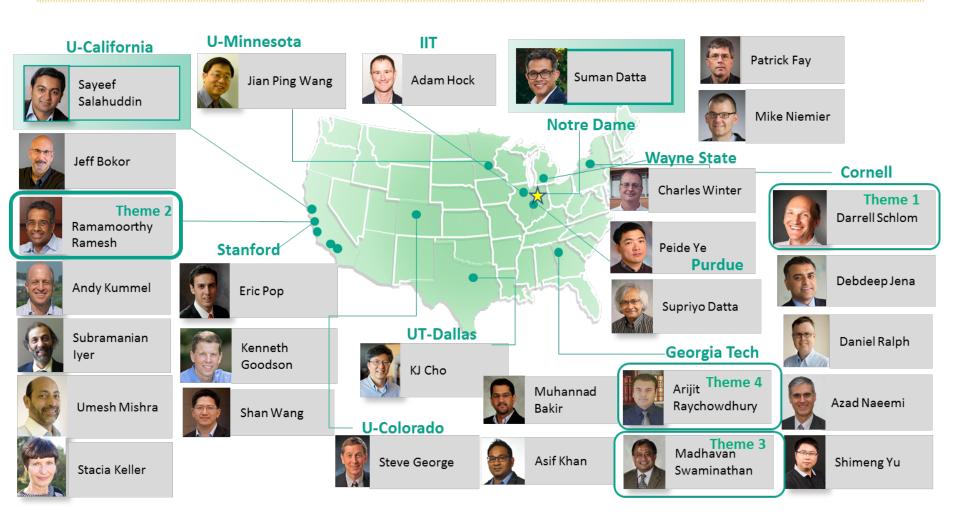

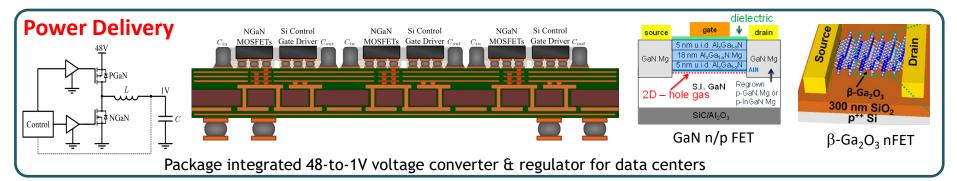

Applications and Systems Driven Center for Energy-Efficient Integrated Nanotechnologies

### ascent.nd.edu

Herding cats or leading All-Star Team

# ASCENT: Applications & System Driven Center on Energy – Efficient Integrated Nanotechnologies

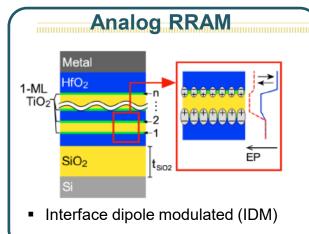

- ♣ BEOL FETs

- Barrier less Vias

- Selectors for 3D memories

- Fine-grained thermal

- ❖ FEOL FETs (NC)

Augment charge with spin

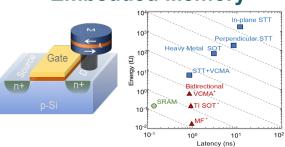

- **♦** SOT MRAM

- VCMA MRAM

- Magneto-electric

- Probabilistic spin devices

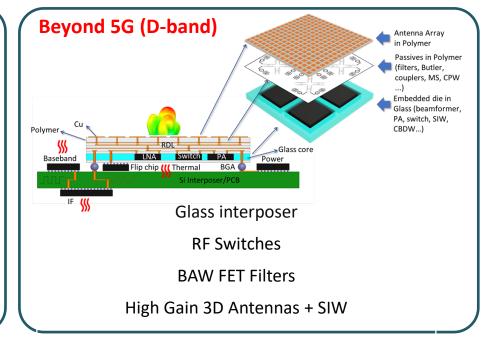

Embrace heterogeneity

- Millimeter-wave packaging

- Chip to chip signaling

- Power delivery

- Reconfigurable RF

- Package-level Thermal

# Compute with memory

- Analog weight cells

- Stochastic compute

- Collective compute

- Secure compute

Design, build and benchmark semiconductor materials, devices, packages and compute fabrics to establish semiconductor technology roadmap for our commercial & defense partners

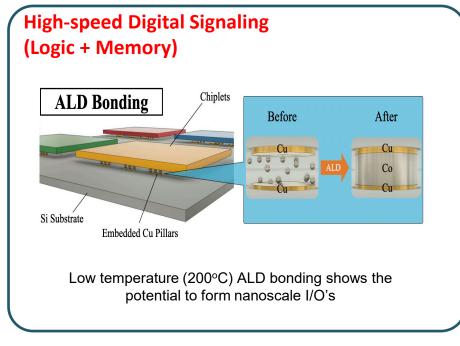

### Monolithic 3D Research Vectors

# Electron Enhanced ALD To Thickness Co(CO)<sub>3</sub>NO on dose Co(CO)<sub>3</sub>NO on dose At dose of the control of the co

- EE-ALD of Cobalt

- Computational growth study

George, Hunter (Colorado, Wayne St)

# Self-aligned Contacts & Vias Cu SAM or Nanofog barrier Cu Co or Rh Contact Selective ALD Silicide Silicide S min 10 min 15 min 20 min

- Hyper Selective ALD of silicide

- Hyper-elective Co (and Ru) ALD

Kummel (UCSD)

Pop, Datta (Stanford, Notre Dame)

5nm thick In<sub>2</sub>O<sub>3</sub> FETs on silicon

### **3D Memory & Selectors**

Selectors for 3D Memory; Mott and Metallon Threshold selectors

### **Sequential M3D Design**

3D SRAM with concurrent row & column data access

3D DRAM

LAYER-1: WDD BLB Wr

Thin cell Design VDD gnd

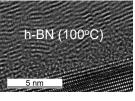

**M3D Thermal Management**

Layered materials (hBN) with anisotropic thermal conductivity

Schlom, Wong, Datta (Cornell, Notre Dame, Stanford)

Datta, Narayanan (Penn St, Notre Dame)

Pop, Goodson (Stanford)

### Heterogeneous Integration Research Vectors

Raychowdhury, Misra (Georgia Tech, UCSB)

Ye (Purdue)

Kummel, Bakir (UCSD, Georgia Tech)

Datta, Fay, Jena, Swaminathan (Notre Dame, Cornell, Georgia Tech)

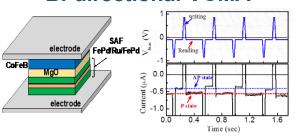

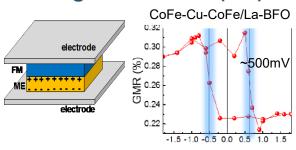

### **Beyond CMOS Research Vector**

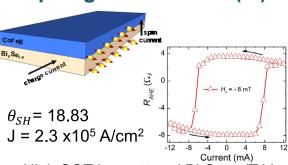

### **Bi-directional VCMA**

- Field-free bidirectional VCMA with SAF

- p-MTJ with J~10<sup>5</sup> A/cm<sup>2</sup> demonstrated

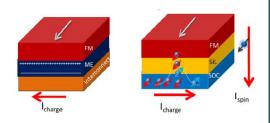

### Magneto-electric (ME)

- Bias Voltage (V) Synthetic Multiferroic

- Voltage-driven bidirectional switching

### **Topological Insulator (TI)**

High SOT in sputtered Bi<sub>x</sub>Se<sub>1-x</sub> (T.I.) and Iridate

JP Wang (Minnesota)

Ramesh (Berkeley)

Wang (Stanford, Minnesota)

### **Embedded Memory**

Logic compatible, high endurance, embedded memory applications

**Spin Logic (Majority gate)**

10aJ class logic operation

Ramesh (Berkeley)

**Probabilistic Computing**

p-bits for Deep Belief Network, Ising machines

JP Wang, Salahuddin (Berkeley)

Salahuddin, Datta (Berkeley, Purdue)

### Merged Logic-Memory Research Vector

### Analog FeFET

Partial Polarization switching, polarization rotation, FE Superlattice

### RRAM CIM (with C-BRIC)

RRAM states

IRS

W<sub>ij</sub> = HRS (-1), IRS (0), LRS (+1) Ternary weight in RRAM cells

CIM accelerators with foundry (TSMC) 1T-1R RRAM

### **FeFET Endurance & Variation**

Understanding fundamental reliability issues in FeFETs

### FeFET CIM (with CRISP)

CIM accelerators (simulation based)

### **NVMExplorer (with ADA)**

Cross-stack Framework for CIM accelerator design

# Lessons Learnt during High-Risk Semiconductor Research

Serendipity happens but it is not luck. It's being in the right place at the right time with the *right training and mindset*

Scaling is not a Law of Physics. It's hard work by scientists and engineers, our ingenuity and audacity to compete and thrive, driven by free market economics

Materials scientists, device physicists, circuit designers, system architects & algorithm experts will collaborate to drive semiconductor *innovations that provide* application and system level benefit. A tsunami of investment in semiconductors in the *United States, Europe and Asia* is coming!

"Such an exponential will continue for a very long time"

# Family

"Families are the compass that guides us. They are the inspiration to reach great heights, and our comfort when we occasionally falter"