# **Impact of Not Planned For**

# Kenneth K. O

#### Texas Analog Center of Excellence & Dept. of ECE University of Texas at Dallas, Richardson, TX

November 11<sup>th</sup>, 2021

Silicon Microwave Integrated Circuits and Systems Research Group

### **Contributors**

Changhua Cao (MediaTek), Eunyoung Seok (Samsung), Brian Floyd (NC State U.), Kihong Kim, Chih-Ming Hung (MediaTek), Tod Dickson (IBM), Jesal Mehta, Wayne Bomstad, Manish Biyani (Intel), Jason Branch, Xiaoling Guo (Murata), Ran Li (IDT), Yanping Ding (Qualcomm), Su Yu (Silicon Labs), Ning Zhang, Dong-Jun Yang, Jose Bohorquez, Myung Hwang, Dan Bravo, Dongha Shim (SNUT), Ruonan Han (MIT), Ibukun Momson (Intel), Yaming Zhang (Apple), Jing Zhang (NXP), Zeshan Ahmad (TI), Navneet Sharma (Samsung), Dae-Yeon Kim (Qorvo), Qian Zhong (MediaTek), Sandeep Kshattry (Raytheon), Pranith Byreddy, Pavan Yelleswarapu, Shenggang Dong (Samsung), Yukun Zhu, Zhe Chen (Southeast U., China), Wooyeol Choi (Oklahoma State U.)

## Outline

- Research turned out to be unexpectedly challenging.

- Research turned out to be unexpectedly much easier.

- Conclusion

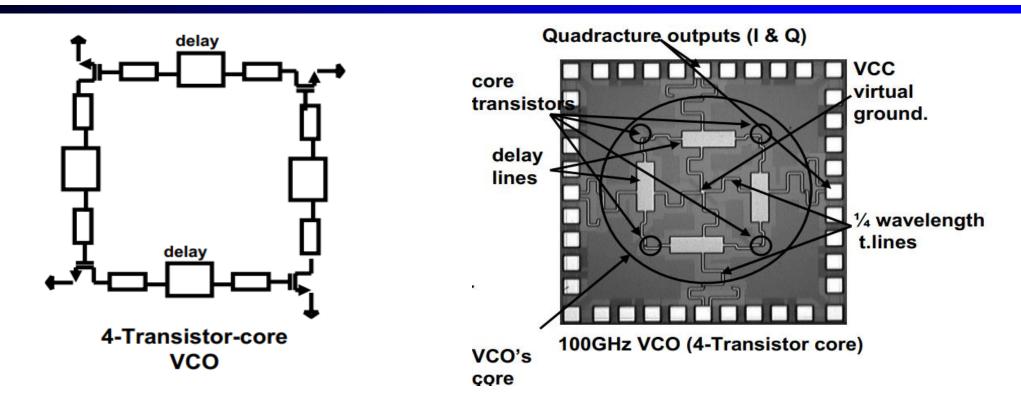

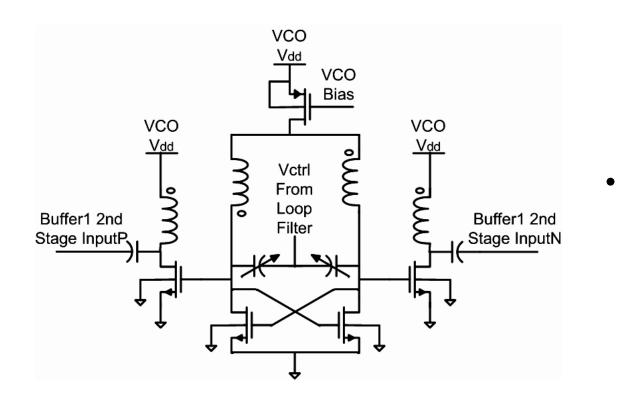

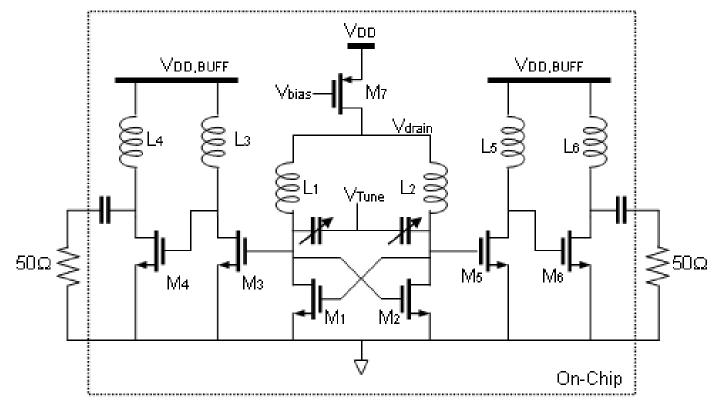

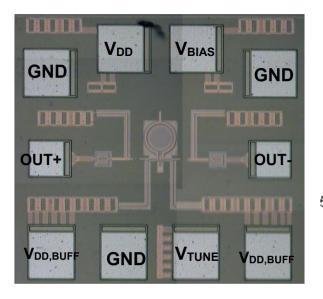

State of art in 2004: 100-GHz oscillation in 90-nm bulk CMOS demonstrated. Measured weak output power (-65 dBm or 0.3 nW) while consuming 100-mW DC power.

Luiz M. Franca-Neto, Ralph E. Bishop, Brad A. Bloechel, "64GHz and 100GHz VCOs in 90nm CMOS Using Optimum Pumping Method," Paper 24.6, International Solid-State Circuits Conference, 2004.

- 1<sup>st</sup> Attempt: Simulations showed that 100-GHz oscillation possible in 130nm CMOS: Taped out and measured. <u>No oscillation.</u>

- 2<sup>nd</sup> Attempt: Must be the transconductance being too low.

Widen the core transistors. Taped out and measured. Once again, no oscillation. Models are good up to frequencies less than 10 GHz. Started to use HFSS.

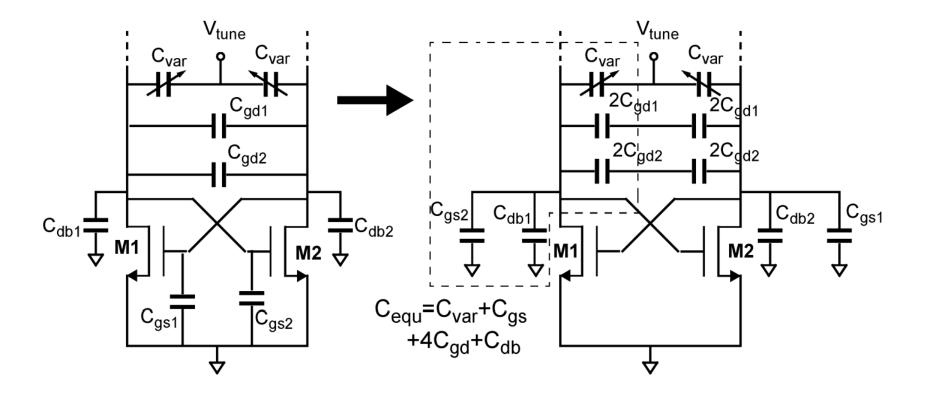

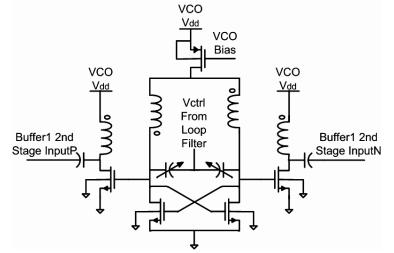

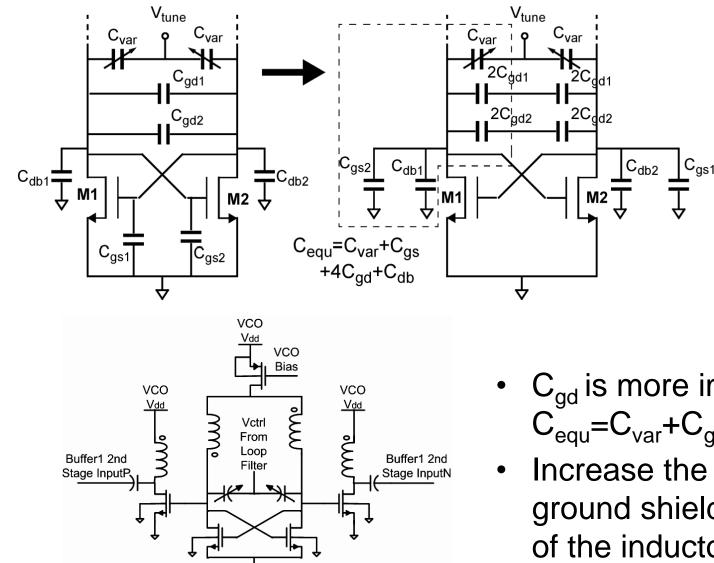

•  $C_{gd}$  is more important due to Miller effect.  $C_{equ}=C_{var}+C_{gs}+C_{db}+4C_{gd}(+C_{ds}+...)$

http://www.sony.net/Products/SC-HP/cx\_news/vol33/featuring.html

$C_{equ} = C_{var} + C_{qs} + C_{db} + 4C_{qd} (+C_{ds} + \dots)$

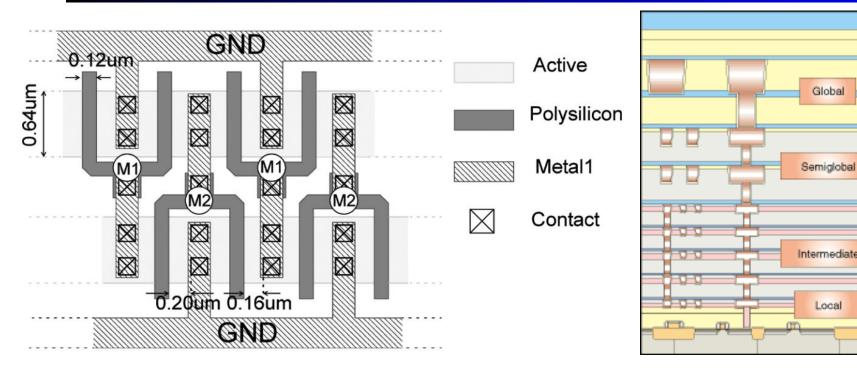

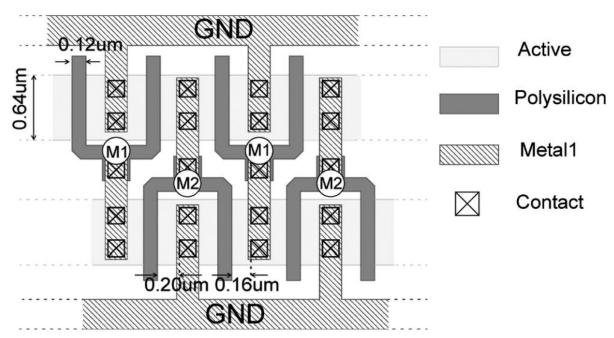

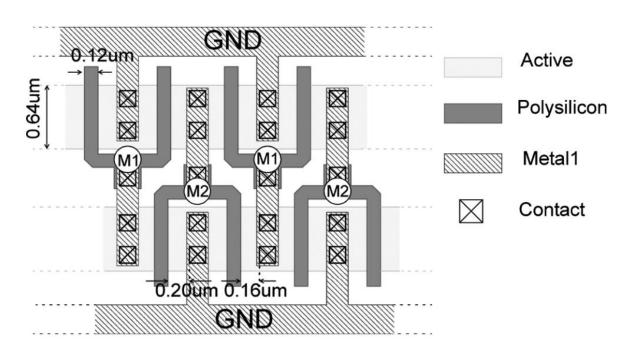

- Layout optimization to lower the capacitance associated with the drain to gate connection.

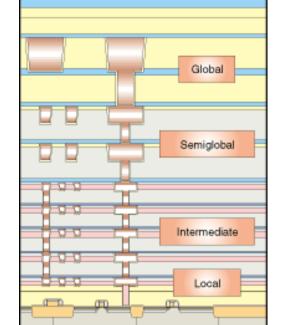

- Metal 1-6 stack for drain to gate connection for drain and source.

- Later on: Metal 1-2 for source connections and Metal 1-3 stack for drain connections.

http://www.sony.net/Products/SC-HP/cx\_news/vol33/featuring.html

- Increase the spacing between gate poly and drain contact/metal to lower  $C_{GD}$  but increases  $C_{DB}$ .

- Optimal gate to polysilicon spacing is 0.16 μm.

$C_{equ} = C_{var} + C_{qs} + C_{db} + 4C_{qd} (+C_{ds} + \dots)$

ullet

http://www.sony.net/Products/SC-HP/cx\_news/vol33/featuring.html Increase the spacing between gate poly and source contact/metal to lower  $C_{GS}$ . Greater flexibility to increase since  $C_{SB}$  is grounded.

• Spacing of 0.20 μm.

$C_{equ} = C_{var} + C_{gs} + C_{db} + 4C_{gd} (+C_{ds} + ...)$

- $C_{gd}$  is more important due to Miller effect.  $C_{equ}=C_{var}+C_{gs}+C_{db}+4C_{gd}(+C_{ds}+...)$

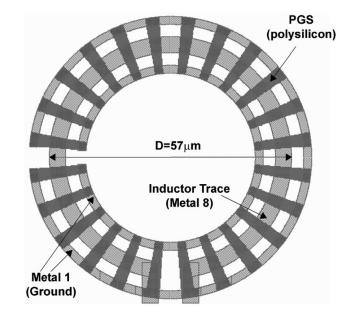

- Increase the spacing between ground bars for the ground shield to reduce the parasitic capacitance of the inductor.

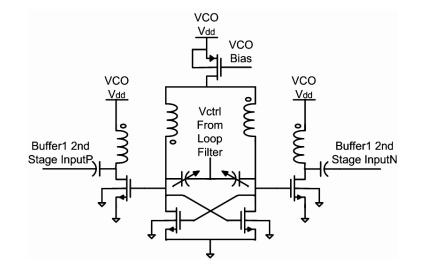

Tapered buffer/isolation stages in order to reduce the load for the main tank.

|              | -                  |                         |                        |                         | -                  |                     |  |

|--------------|--------------------|-------------------------|------------------------|-------------------------|--------------------|---------------------|--|

| Ref          | Frequency<br>(GHz) | Phase Noise<br>(dBc/Hz) | V <sub>dd</sub><br>(V) | P <sub>dc</sub><br>(mW) | Tuning<br>(GHz)    | Technology          |  |

| This<br>work | 59                 | -89@1MHz                | 1.5                    | 9.8                     | 5.8                |                     |  |

|              | 98.5               | -102.7@10MHz            | 1.5                    | 7–15                    | 2.5 <sup>a</sup>   | 0.13-μm CMOS        |  |

|              | 105.2              | -97.5@10MHz             | 1.2                    | 7.2                     | 0.2                |                     |  |

| [2]          | 50                 | -100@1MHz               | 1.3                    | 13                      | 1.0                | 0.25-μm CMOS        |  |

| [3]          | 51                 | -85@1MHz                | 1.0                    | 1                       | 1.0 <sup>a,b</sup> | 0.12-μm CMOS        |  |

| [4]          | 40.7               | -89@1MHz                | 1.8                    | 11.3                    | 6.0                | 0.13-µm SOI<br>CMOS |  |

| [5]          | 103.9              | <-94@10MHz              | 1.5                    | 180                     | N/A                | 90-nm CMOS          |  |

| [9]          | 60.6               | -90@1MHz                | 1.5                    | 21                      | 8.3 <sup>b</sup>   | 90-nm SOI<br>CMOS   |  |

|              | 1                  | 1                       | I                      |                         |                    | 1                   |  |

- ~45 dB higher output power at ~6-7X lower DC power consumption using a less advanced technology.

- Can be frequency tuned.

- Identified techniques to increase the transistor size while maintaining the operating frequency.

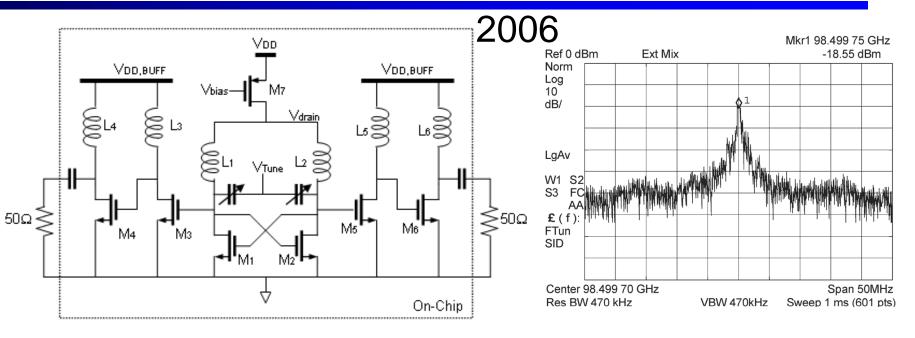

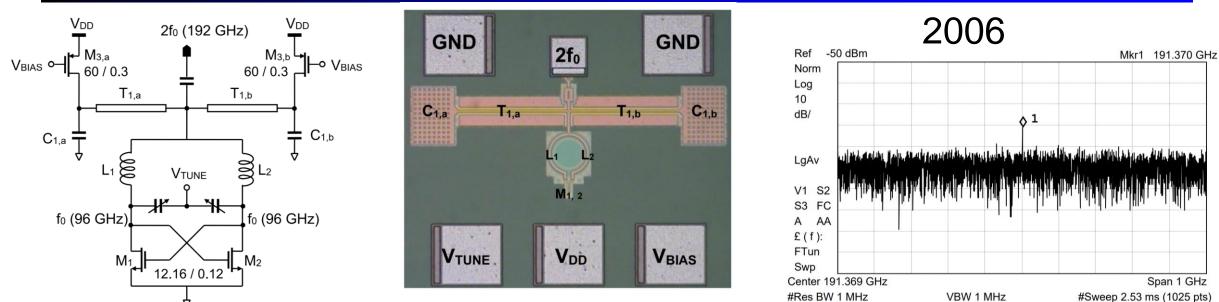

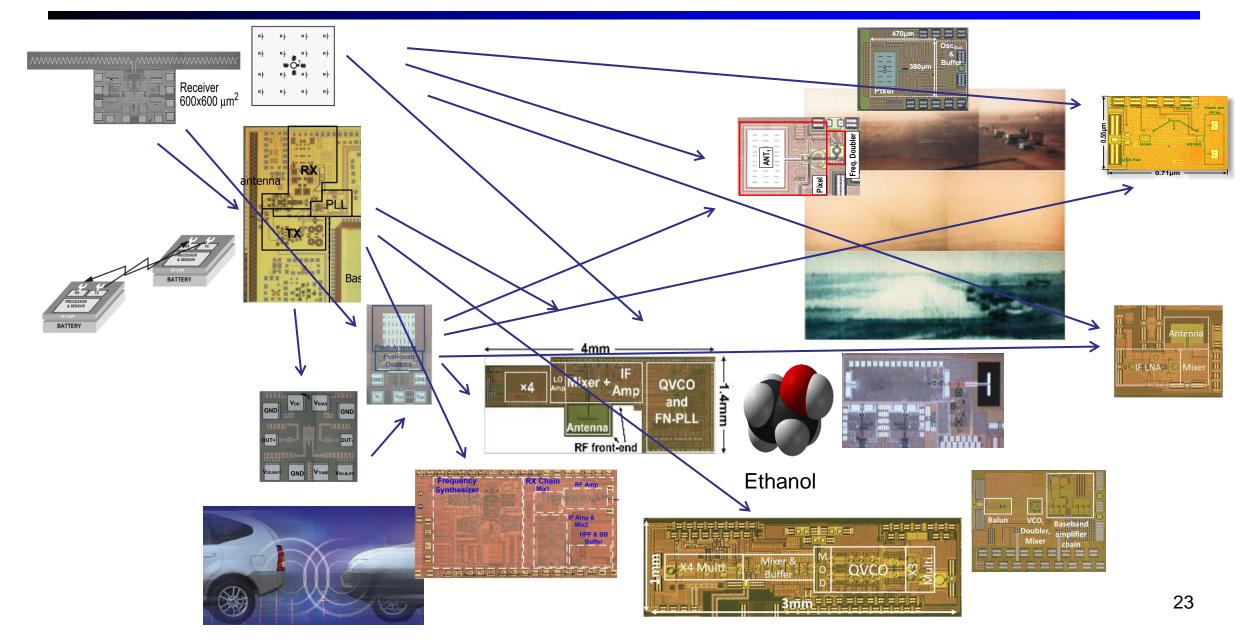

# **192-GHz Signal Generation in 130-nm CMOS**

- 2-push to double the frequency.

- Since no buffer required, the core transistors can be increased for higher fundamental output power.

| Parameters                  |                            |  |  |

|-----------------------------|----------------------------|--|--|

| Output Frequencies (GHz)    | 191.4 – 192.7              |  |  |

| Output Power                | -20 dBm                    |  |  |

| DC Power Consumption        | 17 mW                      |  |  |

| Phase noise (10 MHz offset) | -106 dBc/Hz at the ~95 GHz |  |  |

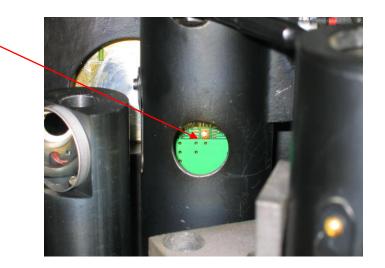

# 410-GHz Signal Generation in 45-nm CMOS

- Fundamental oscillation at 205 GHz.

- 2-Push for frequency doubling.

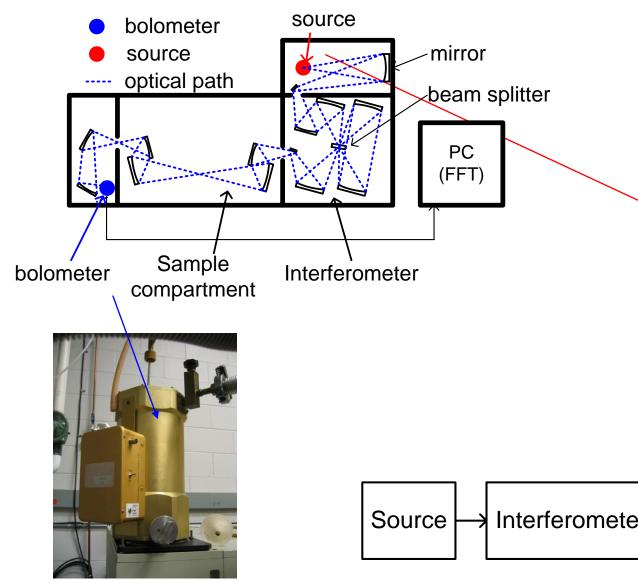

- How to measure??

- Need an on-chip antenna.  $\bullet$

## 410-GHz Signal Generation in 45-nm CMOS

- 1<sup>st</sup> Tapeout: No bond pad opening.

- 2<sup>nd</sup> Tapeout: No signal. Model intended for operation at frequencies less than 10 GHz. HFSS is extensively used.

- 3<sup>rd</sup> Tapeout: Multiple versions with antennas tuned at varying frequencies. (~10 nW of power)

- 4<sup>th</sup> Tapeout: Optimized the circuit at 390 GHz to achieve <u>2 μW</u>.

(Bigger core transistors and metal oxide metal bypass capacitors)

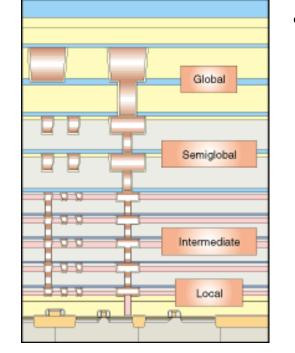

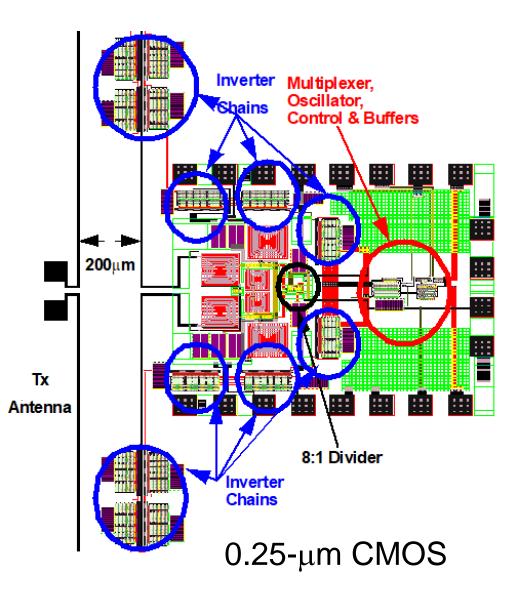

- Clock frequency was expected to be multi-GHz and skew tolerance tighter.

- Chip size is expected to increase to over 2 cm x 2 cm. Need to match the increasing latency to satisfy the decreasing skew tolerance.

- Power consumption of clock distribution was increasing.

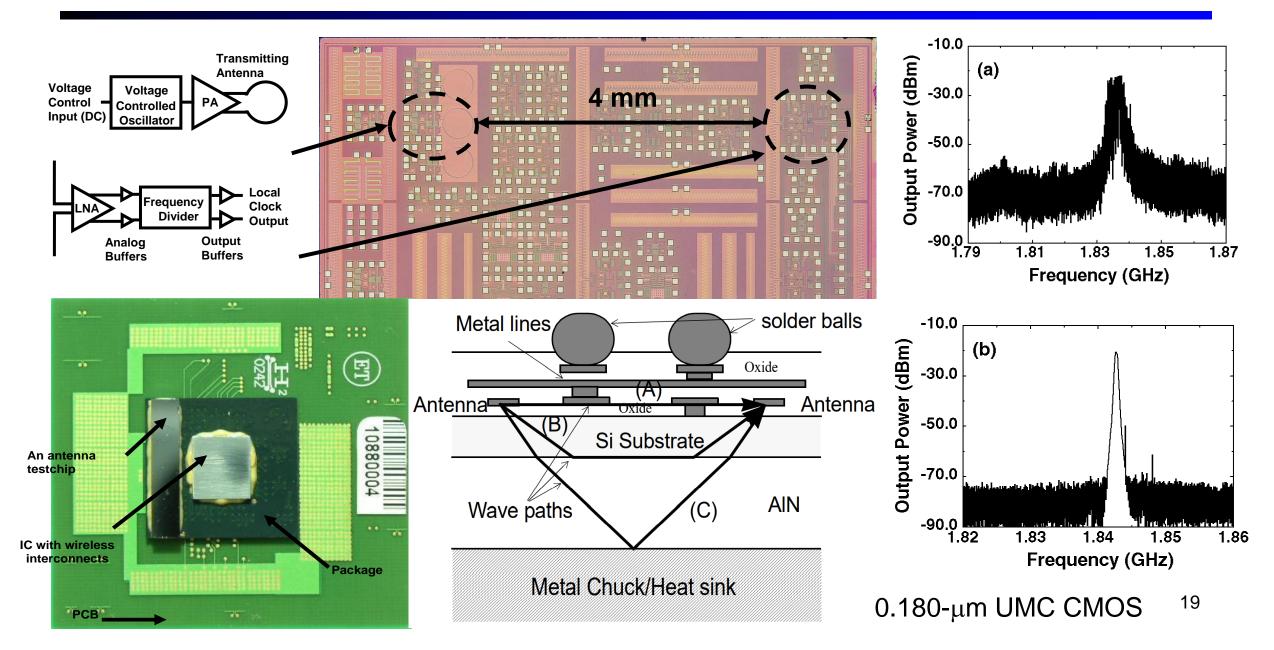

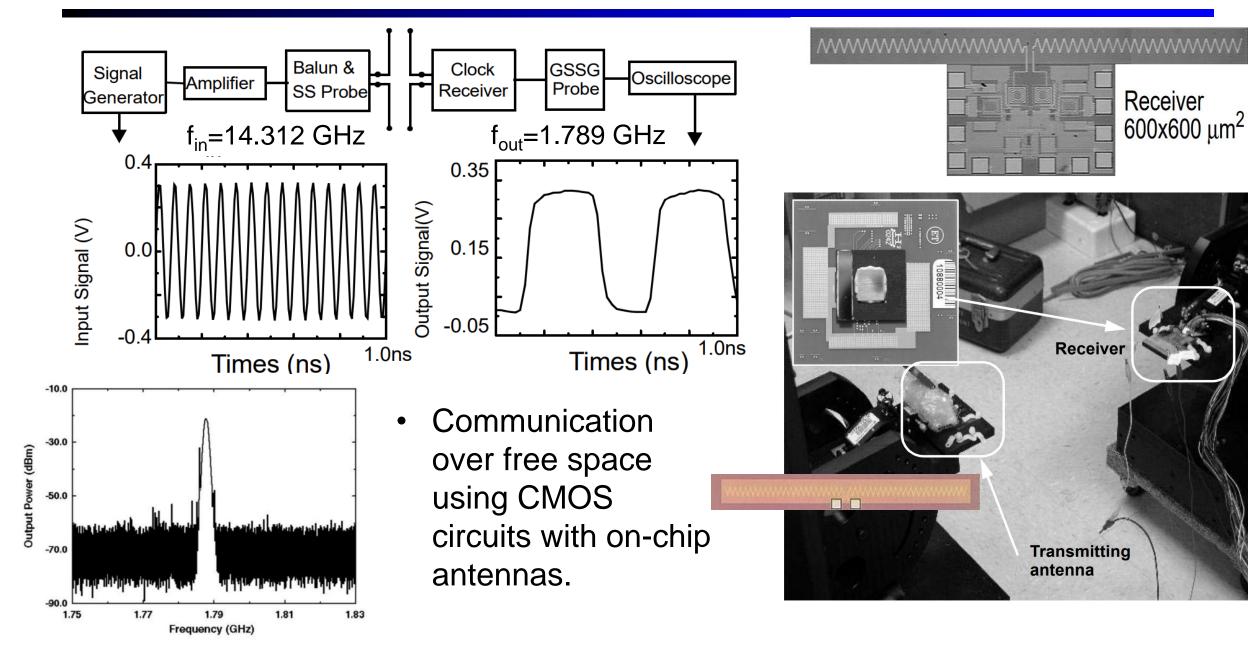

- Reduce the latency by distributing the signal with the speed of light limited delay instead of RC limited delay.

- Investigate if power consumption can be reduced.

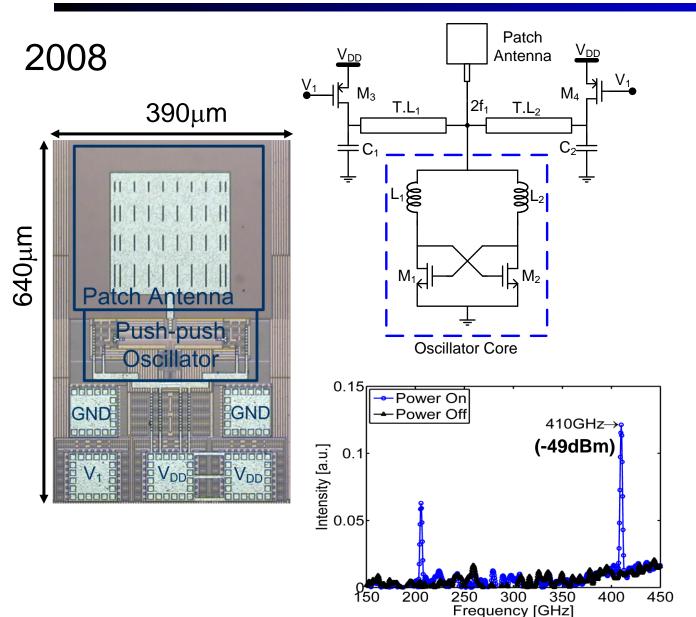

- RFCMOS is struggling to meet the requirements for the 900-MHz cellular applications. Can you build the necessary circuits?

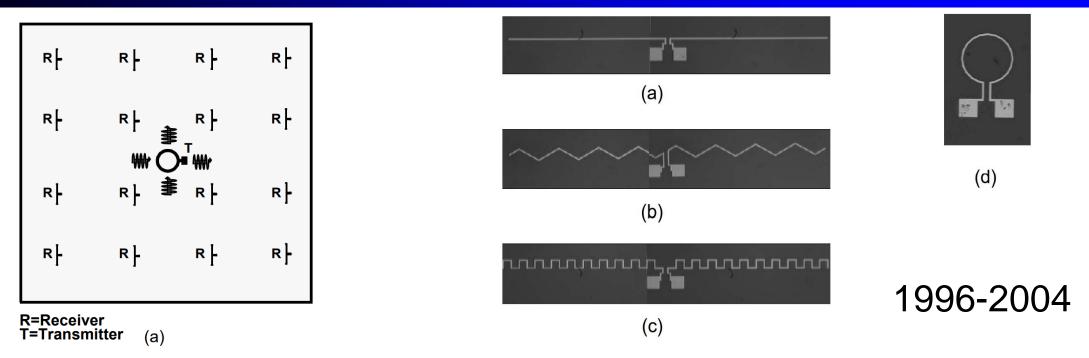

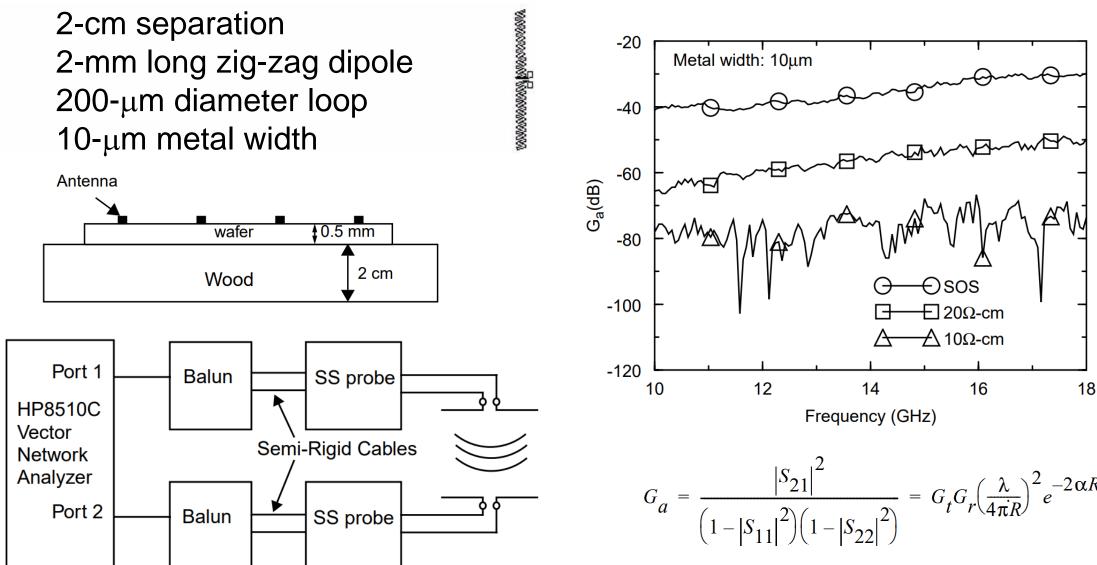

- Can you integrate sufficiently efficient antennas?

- Can you propagate signals within an IC with so many devices and interconnects?

- Can we overcome the interference to the circuits in an IC as well as to the clock by the circuits in an IC?

Measured clock jitter and SNR

| Inj                       | put to Noise Generators | VCO              | <b>Received</b> Clock |                  |

|---------------------------|-------------------------|------------------|-----------------------|------------------|

| Transmit Power to Antenna |                         | 15 dBm           | 15 dBm                | 17.5 dBm         |

|                           | Quiet                   | 0.57%<br>26.4 dB | 0.57%<br>26.4 dB      | 0.41%<br>29.3 dB |

| lition                    | А                       | 0.91%<br>22.4 dB | 0.98%<br>21.7 dB      | 0.59%<br>26.1 dB |

| Noise Condition           | В                       | 1.05%<br>21.1 dB | 0.96%<br>21.9 dB      | 0.76%<br>23.9 dB |

| Noise                     | С                       | 1.37%<br>18.8 dB | 3.20%<br>11.4 dB      | 1.83%<br>16.3 dB |

|                           | D                       | 2.72%<br>12.8 dB | no lock<br>(N/A)      | 3.63%<br>10.3 dB |

| Ena | Enables |                   | Noise Condition                                       |  |  |  |

|-----|---------|-------------------|-------------------------------------------------------|--|--|--|

| E1  | E2      | Label Description |                                                       |  |  |  |

| 0   | 0       | A                 | Small inverter chains on one side switching           |  |  |  |

| 0   | 1       | В                 | All small inverter chains switching                   |  |  |  |

| 1   | 0       | C                 | Small and large inverter chains on one side switching |  |  |  |

| 1   | 1       | D                 | All inverter chains switching                         |  |  |  |

## **Use of Wireless Clock Distribution**

- Demonstrated the on-chip wireless clock.

- Research thread on using wireless communication in network on chip applications.

- Not aware of anybody using this on the Earth.

- On-chip wireless interconnection much easier than anybody has thought!!

#### **Impact of Not Planned For**

## Conclusion

- Failure in planning

- Failure in understanding the difficulties

- Success

- Progress toward goals

- Unexpected learning

- New research directions

- Not planned for is necessary for successful research

- More open to trying out new ideas and keep asking whether the perceived limitations are fundamental or not.