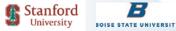

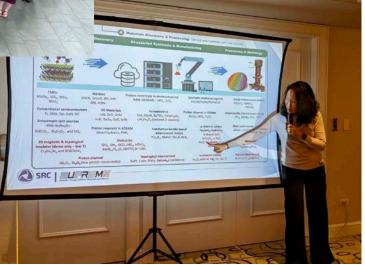

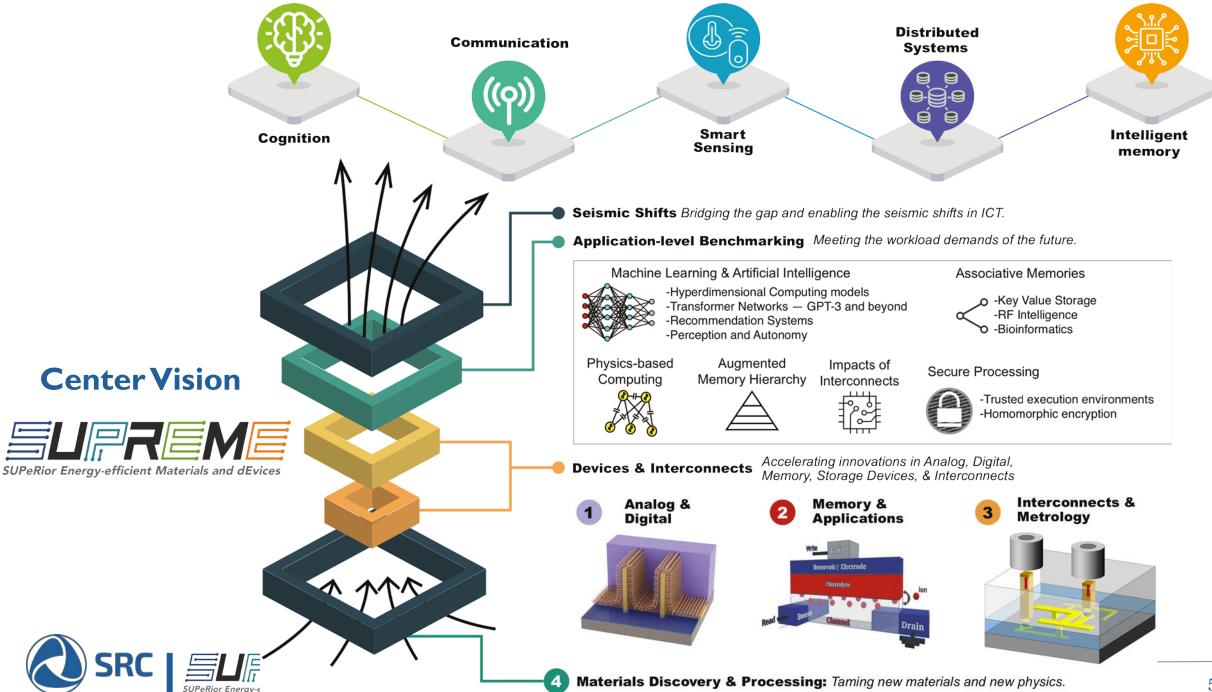

## **SUPeRior Energy-efficient Materials and dEvices**

April 24, 2024

SRC Leadership F2F Meeting, Samsung @ San Jose

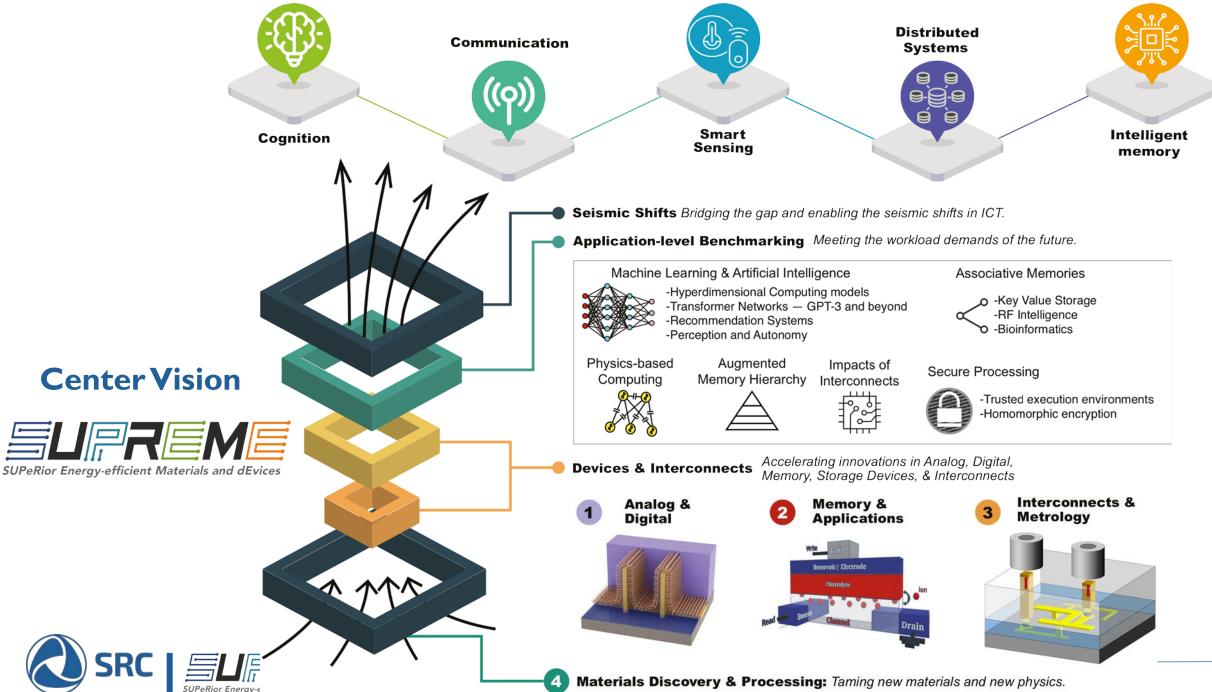

Grace Huili Xing (Cornell), Center Director

Tomás Palacios (MIT), Co-Director

Chris Hinkle (ND), co-Lead on High-Throughput

Elton Graugnard (BSU), Thrust Lead on Advanced Processing

Thomas Dienel (Cornell) Managing Director, Jenna LaMendola (Cornell) Administrative Assistant

TEXAS Rensselaer

## **SUPREME Goals and Accomplishments—Year 1.3**

| Goal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Accomplishment                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1. Center Management</b> : Ensure that all partners meet the 95% spending goal annually, establish subawards timely, enable purchase of capital equipment to provide unique tools and capabilities for future success of the center, establish Pillar Science to disseminate all results, create a center website and newsletters for outward facing communication, and effective communication both within and outside the Center on job opportunities, broadening participation, enable collaboration with other JUMP2.0 centers by creating seed funds, annual PI meeting & review etc              | <ul> <li>✓ Accomplished</li> <li>✓ New: Semi-annual Center <u>Newsletters</u> are planned,<br/>and the 1st sent in January 2024; Inter-center <u>Seed</u><br/><u>funds</u> created, proposals are ready for evaluation</li> </ul> |

| <b>2. Team Collaboration (PIs and students)</b> : Enable collaborative atmosphere for PIs and their groups to be aware of each other's work, broaden participation on all levels though center-wide initiatives, and to develop intracenter collaboration across thrusts and individual projects.                                                                                                                                                                                                                                                                                                         | <ul> <li>Accomplished. We are at ~180 students and<br/>postdocs; New: Established Grad travel funds to<br/>carry out research in labs of other Center PIs</li> </ul>                                                              |

| <b>3. Team Collaboration (Liaisons, PIs, and students; other centers):</b> Establish a culture that liaisons are extended researchers and mentors of the Center. Ensure that Liaisons and PIs are well-connected, including all team members (students, postdocs, etc.) to ensure a smooth exchange of ideas and facilitate outreach to other JUMP 2.0 centers for joint interest and expertise.                                                                                                                                                                                                          | <ul> <li>Excellent progress made; topic-focused meetings<br/>help to increase coherence and connections<br/>between materials and device projects; New: Seed \$</li> </ul>                                                        |

| <b>4. The SUPREME Materials Palette</b> : The materials palette is the unique identity of SUPREME, central to all aspects of the Center research thus most effective in connecting all projects, all researchers, all liaisons and research methods. Learn how to manage a dynamic materials palette, implement the cycle of materials discovery combining theoretical predictions, experimental realization, and thorough characterization to expand or down-select the materials palette. Update and present the updated Materials Palette at the annual center reviews, or other venues if applicable. | <ul> <li>✓ Excellent progress made</li> <li>✓ Top Goal for Year 2: Continuously updating the materials Palette, single document listing metrics</li> </ul>                                                                        |

| <b>5. New research methodologies:</b> Implement new ways of research including machine learning and artificial intelligence (ML/AI) approaches towards high-throughput methods and automated materials discovery, explore inverse design for device design whenever applicable.                                                                                                                                                                                                                                                                                                                           | <ul> <li>✓ Good progress made</li> <li>✓ Top Goal for Year 2: to organize topical workshops</li> </ul>                                                                                                                            |

## Highlights – Year 1.3

#### I. Growth of Center during year 1.3

- Students and Postdocs joined: 185

- Sponsor Liaisons at SUPREME projects: 107

- II FT hires, 15 interns at sponsors

#### 2. Annual Review August 2-3, 2023

• 165 attendees at Cornell University

#### 3. Annual Review June 11-12, 2024

- To be hosted at MIT, Building 45

- Planning for 150 on-site participants

#### 4. Liaison Meetings weekly-exception apply

- Rotating through Thrusts/Topics of SUPREME

- Held 36 meetings, presentation materials on Pillar Science (TOC in Notes)

- At alternating times to balance time zones and availability

#### 5. Broadening Participation

- Two BP Champions guide SUPREME's efforts

- Two awards established since 2023Q2/Q3

- SUPREME Undergraduate Microelectronics Fellows (7 awarded)

- SUPREME Undergraduate Travel Grant (4 awarded)

- Total number of undergrads working on SUPREME projects: 24

#### 2024 April - PI meeting

- 6. Publications (on Pillar Science): 130+

- **7. Keynotes: 70+**

- 8. Awards: 25+

### **24 Undergraduate Students**

**Deniz Erus (MIT)**

Jack Coyle (RPI)

Yufan Feng (Cornell)

**Thomas Hieber (Notre Dame)**

Kathryn Zhang (Cornell)

Zach Erling (Notre Dame)

Sophia Chou (Notre Dame)

Sivagya KC (Boise)

**Finley Donachie (RPI)**

Husayn Mukadam (RPI)

Emma Sponga (RPI)

Andi Qu (MIT)

**Michelle Campbell**

(Northwestern)

**Clayton O'Dell** (Notre Dame)

**Andrew Hennessee** (Notre Dame)

Anna Arnett (Notre Dame)

**Ambrose Yang (Cornell)**

Tomas Kraay (Cornell) Molly Sullivan (Notre Dame)

**Benjamin Bailey (Boise)**

**Michael Bhopaul (MIT)**

Luis Martinez (MIT)

## Lowlights in Year 1 & improvements in Year 2

#### I. Growth of Center during year I

- I. Slow process of completing subawards (last finalized October 2023)

- 2. Need to help improve PI's KPI, especially for those who are new to SRC - improvements are expected in Year 2 thanks to Adam Knapp to present on KPI in 2024QI!

#### 2. Varying efficiency of Liaison Meetings

- 1. Improve schedule to achieve larger Liaison attendance – potentially consider a fixed time over 2 alternating times

- 2. Encourage student attendance

- 3. Continue combination of deep dive presentations and short updates

- 4. Move beyond thrust boundaries with focus on topical areas

#### 3. Leveraging resources

1. Pls attempted to access the HPC systems via the DOD high-performance computing modernization program (HPCMP), but clearance seems to be a bottleneck

#### 4. Meaningful connections with other JUMP 2.0 center to improve benchmarking & understand impacts

- I. Need to be driven by PIs' genuine research needs Seed funds help spur interests and converge topics

- 2. Pls need to have bandwidth incentive helps

#### Soliciting help from the SAB!

#### **1. Seed funds to be evaluated by mid-May 2024** SUPREME – PRISM

SUPREME – CHIMES

- SUPREME CUBIC

- SUPREME CoCoSys

2. Our **NSF REU proposal** was strong but NSF said "insufficient funds at NSF" ....

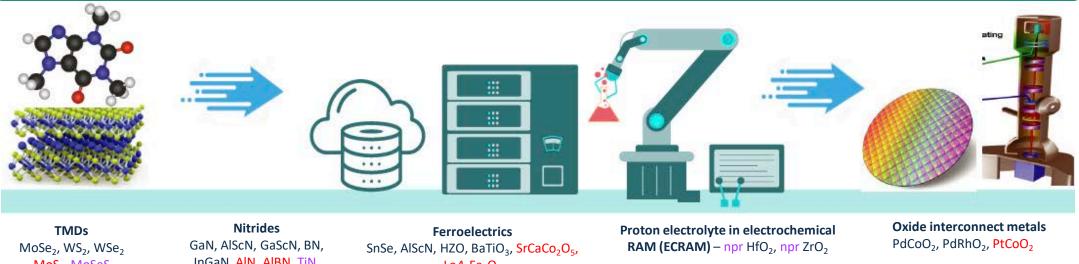

### Year 2 - Top Plans

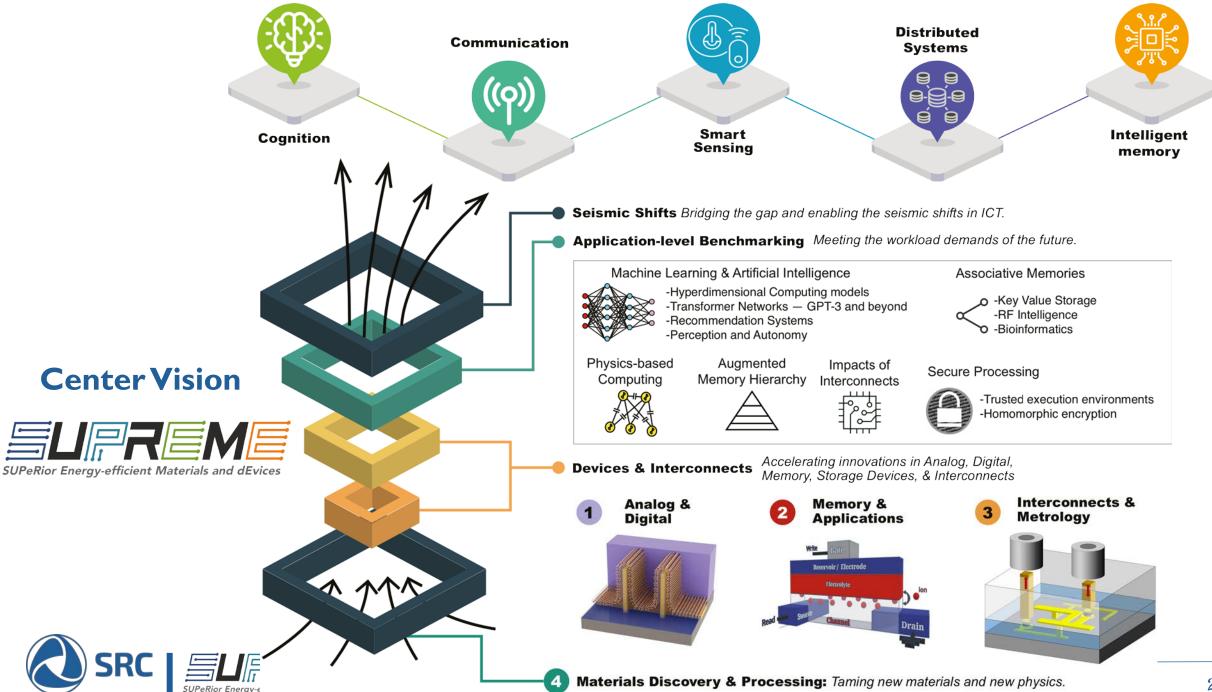

Materials Discovery & Processing: Taming new materials and new physics.

N-channel oxides

In<sub>2</sub>O<sub>2</sub> with W, Mg, Sn, Ga, Ti

**Accelerated Materials Discovery**

**AI-assisted Synthesis & Manufacturing**

**Processing & Metrology**

**1. Implement and improve fail-fast approaches 2. Identify target demonstrations to focus center** tals achievements (seed \$ with system centers) als Conven Si. Anisot 3. Understand system-level impacts  $PdCrO_2$ ,  $B_{12}\Pi_2 \cup_7$ , and  $\Pi \cup_2$ K-doped SnU, SrPd<sub>2</sub>U<sub>4</sub>, a-PdU **Dielectrics** PdO, BaaPbWOg-(not BEOL) **Topological interconnect** 2D magnetic & Molecules

GaPt, CoSn, NbAs, CeCoIn<sub>5</sub>? (oxidation)

Proton channel:

$Nb_2O_5$ ,  $Ta_2O_5$  (low proton conductivity)

topological insulator (demo only – low T):  $Ge_{2}$  Te<sub>6</sub> and BiSbTeSe<sub>2</sub> SiO<sub>2</sub>, SiN<sub>x</sub>, SiCO, HfO<sub>2</sub>, HfZrO<sub>2</sub>. BaHf<sub>0.6</sub>Ti<sub>0.4</sub>O<sub>3</sub> (BHTO) (k~150)

$Ru(pap)_3(PF_6)_2$ ,  $Ru(bpy)_3(PF_6)_2$

III-Vs on Si, graphene

## **Defining feature of SUPREME**

**Accelerated Materials Discovery**

#### Al-assisted Synthesis & Manufacturing

#### **Processing & Metrology**

Intermetallic interconnect metals VPt<sub>2</sub>, MoNi<sub>2</sub>, Nilr<sub>3</sub> CoPt

> **Conductive boride-based** interconnect metals YCo<sub>3</sub>B<sub>2</sub>, NbFeB, Mn<sub>2</sub>B, ReB<sub>2</sub>

**Topological interconnect** GaPt, CoSn, NbAs, CeCoIns (oxidation), FeSn, Coln<sub>3</sub>, Coln<sub>2</sub>, NiTe, Rhln<sub>2</sub> (high R in NWs)

**Optical interconnect** III-Vs on Si, graphene, TMDs, Nitrides, BTO, SnSe

MoS<sub>2</sub>, MoSeS

**2D** Materials AIN. ZnO. SnSe h-Bi, GeSe, GeS (low h mobility), SnTe

Conventional semiconductors Si, SiGe, Ge, GaN, SiC

**Processing Materials Organics**, ASD Resist

**Materials for Ohmic Contacts**

InGaN, AIN, AIBN, TiN, AlLaN, AlYN

n-channel oxides In<sub>2</sub>O<sub>3</sub> with W, Mg, Sn, Ga, Ti, Zn, Ta,  $Ga_2O_3$

p-channel oxides Ta2SnO6, BaBiTaO6 K-doped SnO, SrPd<sub>3</sub>O<sub>4</sub>, a-PdO, PdO, Ba<sub>2</sub>PbWO<sub>6</sub>-(not BEOL by MBE)

**Thermal materials**

BN, AIN, diamond

LaA<sub>2</sub>Fe<sub>3</sub>O<sub>8</sub> (ordered O vacancy), Ln<sub>4</sub>Pn<sub>2</sub>O

> **Dielectrics** Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, SiN<sub>x</sub>, SiCO, HfO<sub>2</sub>, HfZrO<sub>2</sub>, BN, BaHf<sub>0.6</sub>Ti<sub>0.4</sub>O<sub>3</sub> (BHTO) (k~150), SiC, AlN, hr-Si

**Anisotropic spin sources** PtO, Sr<sub>2</sub>Ru<sub>2</sub>O<sub>2</sub>-(not yet grown) PdCrO<sub>2</sub>, Bi<sub>2</sub>Ir<sub>2</sub>O<sub>7</sub>, and IrO<sub>2</sub> (low efficiency), SrRuO<sub>3</sub>

Synthetic antiferromagnets FeCoB/Pt/Ru/Pt/FeCoB

Weyl semi-metals, Heusler alloys - Co<sub>2</sub>MnGa, Mn<sub>3</sub>Sn, Mn<sub>3</sub>Ir

**ECRAM** channel

MoO<sub>3</sub>, WO<sub>3</sub>, V<sub>2</sub>O<sub>5</sub>, Nb<sub>2</sub>O<sub>5</sub>, Ta<sub>2</sub>O<sub>5</sub>, IGZO

Proton reservoir in ECRAM

Metal hydrides, PdH,

Molecules

$Ru(pap)_{3}(PF_{6})_{2}$ ,  $Ru(bpy)_{3}(PF_{6})_{2}$

2D magnetic & topological

insulator (demo only – low T)

Cr<sub>2</sub>Ge<sub>2</sub>Te<sub>6</sub> and BiSbTeSe<sub>2</sub>

Materials in the proposal; Materials added/tabled in Year 1; Materials added/tabled in Year 2

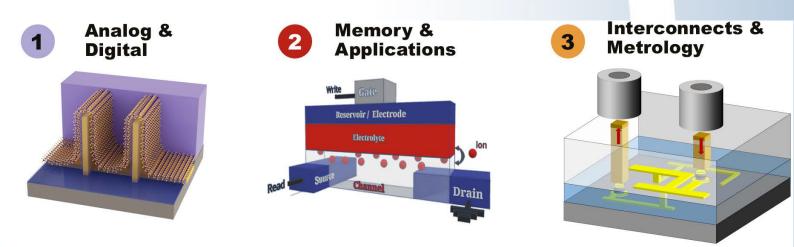

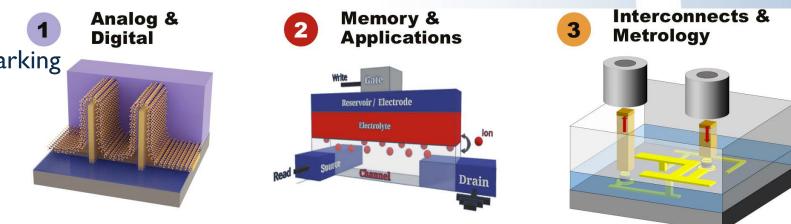

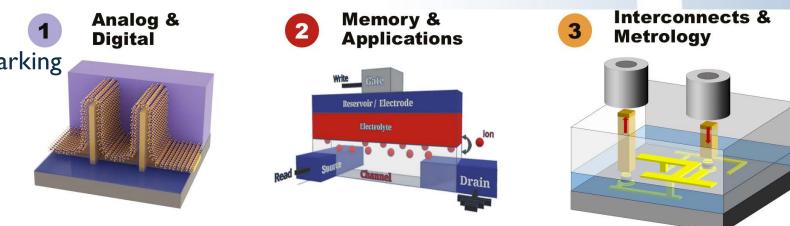

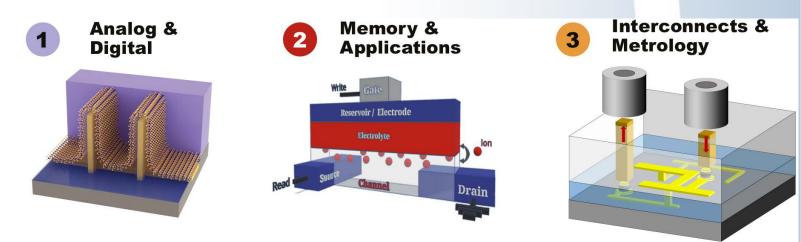

## **Topics in SUPREME**

- I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- **10. High-throughput materials discovery**

- **II. Advanced processing**

- **12. High-k dielectrics & ferroelectrics**

Materials Discovery & Processing: Taming new materials and new physics.

# **Topics in SUPREME (highlighted today)**

### I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- **10. High-throughput materials discovery**

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

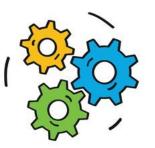

## Topic: 2D materials & devices for high-density logic and memory

- 1. Pls: Feliciano Giustino, Jing Kong, Tomas Palacios, Eric Pop, Farhan Rana, Elton Graugnard, Steve George

- 2. Tasks: 3137.001, 3137.028, 3137.029, 3137.030, 3137.031, 3137.043

- 3. Application: High-density logic and memory

- 4. Objectives:

- a. To identify and realize 2D materials with high carrier mobility

- b. To develop synthesis strategies to obtain high quality 2D materials at BEOL compatible temperatures

- c. To demonstrate multi-channel 2D-nFET outperforming silicon at 1 nm node and beyond

- d. To improve 2D-pFET doping, lower defects, compare 1L vs. 2L, target I<sub>D</sub> > 750  $\mu$ A/ $\mu$ m, R<sub>C</sub> < 200  $\Omega$ · $\mu$ m

#### 5. SOTA:

- a. Mobilities of TMDs are < 50-100 cm<sup>2</sup>/Vs at RT

- b. Bi ohmic contacts to  $MoS_2$  with low contact resistance (123  $\Omega \cdot \mu m$ ) and high current density (1135  $\mu A/\mu m$ )

- c. 8" wafer-scale low-temperature (<300 °C) by MOCVD

- d. Gate-all-around transistor based on MoS<sub>2</sub> nano-ribbon (TSMC 2022)

- e. 2D-pFETs are far behind 2D-nFETs

- 6. Approaches with feedback loops:

- a. High-throughput search for high-mobility candidates using the ab initio Boltzmann transport equation

- b. ML-advised automation of 2D materials synthesis & characterization

- c. Improve p-type channel material quality

- d. Processing one atomic layer at a time: atomic layer etch of 2D materials

- e. 8" large-wafer highly-scaled devices (< 8 nm), self-aligned source/drain with multi-channels formed with one etching step

## Topic (achievements): 2D materials & devices for high-density logic and memory

# **Topics in SUPREME (highlighted today)**

### I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- **10. High-throughput materials discovery**

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

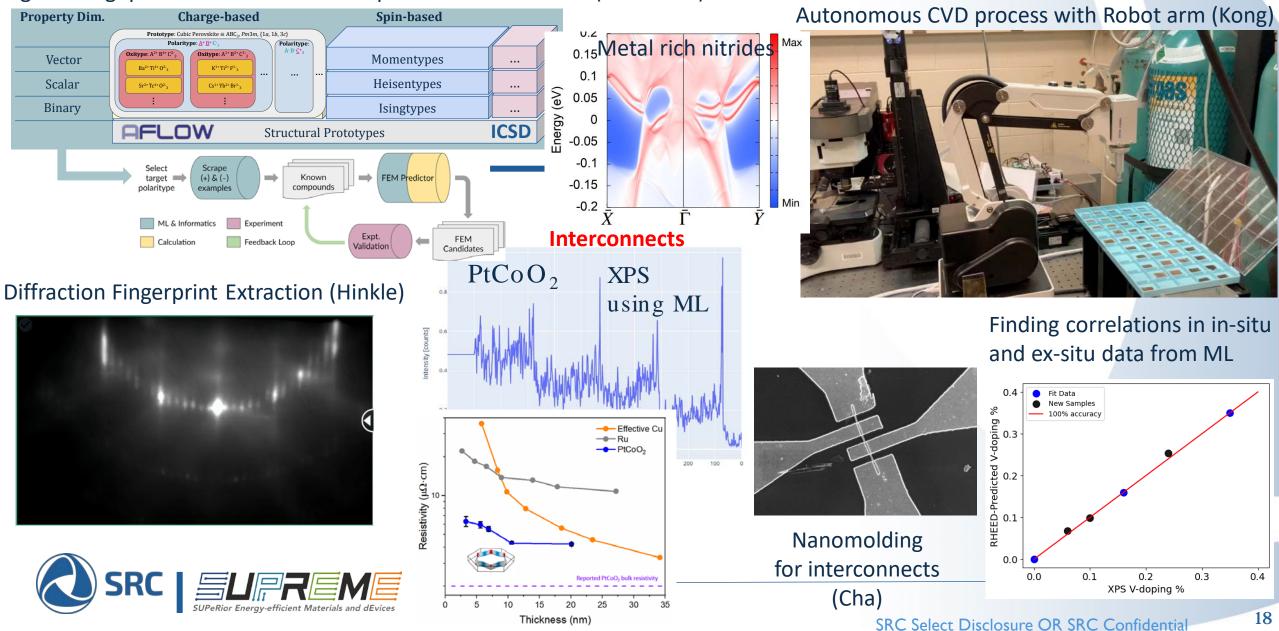

## **Topic: High-Throughput Materials Discovery**

- 1. Pls: Christopher Hinkle, Jing Kong, James Rondinelli, Judy Cha, Farhan Rana

- 2. Tasks: 3137.020, 3137.025, 3137.030, 3137.037, 3137.038, 3137.046

- **3. Application:** Develop new synthesis, characterization, and predictive methods to accelerate materials discovery

- 4. Objectives:

- a. To identify new materials for interconnects, oxide semiconductors, and ferroelectrics

- b. To develop deep learning methods for accelerated materials characterization

- c. To develop new synthesis routes and automated synthesis

- d. To demonstrate superior electronic materials on an accelerated timeline

#### 5. SOTA:

- a. Linear trial and error, expert intuition, and grid search experiment design

- b. 10 years to optimize new electronic materials

#### 6. Approaches with feedback loops:

- a. First-principles computational search and design of new materials (Rondinelli)

- b. High-throughput thin film materials synthesis (Hinkle)

- c. Deep learning-aided materials characterization (diffraction, XPS, microwave reflectometry) (Hinkle)

- d. Automated 2D material synthesis with AI guided characterization and experiment design (Kong)

- e. Direct high-throughput wire synthesis through nanomolding (Cha)

- f. High-throughput defect spectroscopy using THz (Rana)

### **Topic (achievements): High-Throughput Materials Discovery**

High-throughput ML+DFT workflow to predict new materials (Rondinelli) Machine Learning Aided Material Discovery

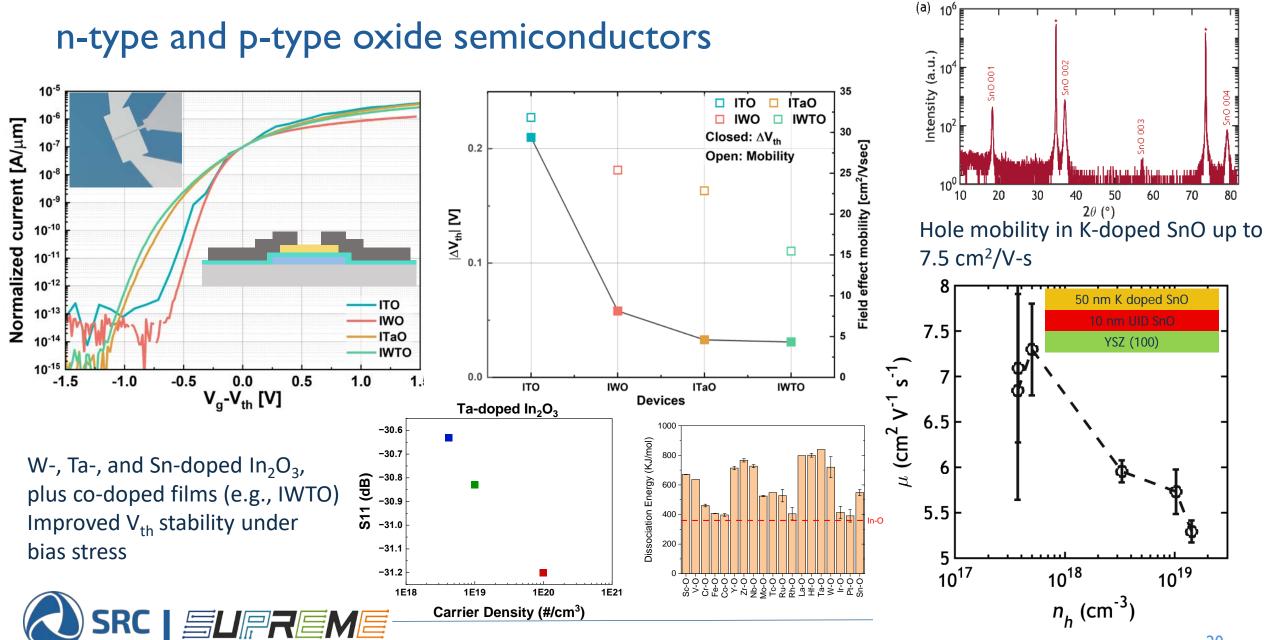

## Topic: Oxide materials & devices for high-density logic and memory

- 1. Pls: Christopher Hinkle, Kai Ni, Asif Khan, Darrell Schlom, Grace Xing

- 2. Tasks: 3137.011, 3137.013, 3137.037, 3137.033

- Application: Develop n-type and p-type oxide semiconductors with mobility >30 cm<sup>2</sup>/V-s with better reliability

- 4. Objectives:

- a. Fabricate In<sub>2</sub>O<sub>3</sub>-based amorphous oxide semiconductors with various dopant/alloy species for nchannel

- b. MBE of K-doped SnO and PdO for p-channel

- c. Optimize processing conditions for each composition

- d. Compare performance vs. stability for different compositions

- e. Downselect most promising materials for further optimization/improvement

- 5. SOTA:

- a. IWO and  $In_2O_3$  bilayer films with mobility >30 cm<sup>2</sup>/V-s, but greater than 0.2 eV  $\Delta V_{th}$  under bias stress

- b. SnO and CuO with mobility <10 cm<sup>2</sup>/V-s

- 6. Approaches with feedback loops:

- a. High-throughput thin film materials synthesis including processing spread (Hinkle)

- b. MBE of K-doped SnO and PdO with Hall measurements (Schlom)

- c. Device fabrication on promising films to assess carrier density and mobility (Hinkle, Ni, Khan)

- d. BTS measurements and stability assessment (Hinkle, Ni, Khan)

- e. SMM measurements for contactless mobility measurements (Hinkle)

## Topic (achievements): Oxide materials & devices for logic and memory

# **Topics in SUPREME (highlighted today)**

### I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- **10. High-throughput materials discovery**

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

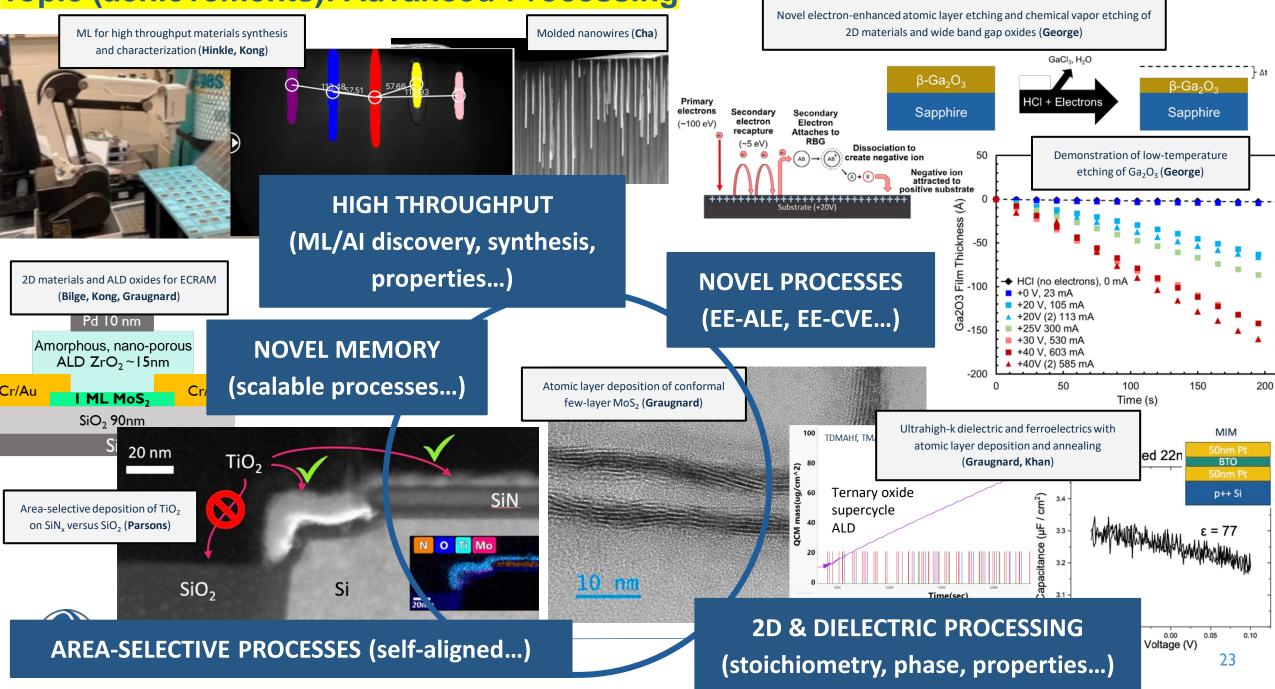

### **Topic: Advanced Processing for logic and memory device materials**

- 1. PIs: Jing Kong, Elton Graugnard, Steve George, Greg Parsons, Judy Cha, Asif Khan, Chris Hinkle, Andy Kummel (CHIMES)

- **2.** Tasks: 3137.011, 3137.020, 3137.038, 3137.041, 3137.029, 3137.030, 3137.031, 3137.039, 3137.040, 3137.042, (CHIMES: 3136.020, 3136.022)

- 3. Application: Integration of materials into logic and memory devices against manufacturing constraints

- 4. Objectives:

- a. To develop synthesis strategies to obtain high quality 2D materials at BEOL compatible temperatures with thickness/layer control

- b. To enable ALD of ferroelectric materials beyond HZO and ultrahigh-k dielectrics

- c. To establish automated and high-throughput materials synthesis and characterization to accelerate processing for improved properties across materials classes (interconnects, dielectrics, 2D materials, etc.)

- d. To enable advanced integration strategies through area-selective deposition and etching

- 5. SOTA:

- a. 200 mm wafer-scale TMDs with low-temperature (<300 °C) by MOCVD and RT mobilities of TMDs are < 50-100 cm<sup>2</sup>/Vs (SUPREME)

- b.  $300 \text{ mm MoS}_2 < 300 \text{ °C}$  by ALD with nanoscale grain size and mobility  $< 1 \text{ cm}^2/\text{Vs}$  (industry R&D)

- c. Automated processing now applied to films and structural property correlation (SUPREME)

- d. Layer-by-layer etching of 2D materials demonstrated (SUPREME)

- e. Inherent area-selective processing without small molecules on chemically distinct surfaces (SUPREME)

- f. Ferroelectric films by PVD, limited ferroelectric oxides by ALD

- 6. Approaches with feedback loops:

- a. MOCVD of 2D materials with atomic layer etching for thickness control (Kong/George)

- b. ML-advised automation of 2D materials, novel interconnects and topological materials synthesis & characterization (Hinkle/Kong/Cha)

- c. Area-selective deposition on chemically-similar surfaces and for 2D materials by ALD (Parsons/Graugnard)

- d. Ferroelectric/dielectric ALD process development with atomic layer annealing (ALA) (Graugnard/Khan/Kummel)

- e. Proton transport solid state electrolytes and 2D channel materials for ECRAM (Bilge/Kong/Graugnard)

## **SUPeRior Energy-efficient Materials and dEvices**

Grace Huili Xing (Cornell), Center Director Tomás Palacios (MIT), Co-Director Chris Hinkle (ND), co-Lead on High-Throughput Elton Graugnard (BSU), Thrust Lead on Advanced Processing Thomas Dienel (Cornell) Managing Director, Jenna LaMendola (Cornell) Administrative Assistant

## Highlights – Year 1.3

#### I. Growth of Center during year I.3

- Students and Postdocs joined: 185

- Sponsor Liaisons at SUPREME projects: 107

- II FT hires, 15 interns at sponsors

#### 2. Annual Review August 2-3, 2023

• 165 attendees at Cornell University

#### 3. Annual Review June 11-12, 2024

- To be hosted at MIT, Building 45

- Planning for 150 on-site participants

#### 4. Liaison Meetings weekly-exception apply

- Rotating through Thrusts/Topics of SUPREME

- Held 36 meetings, presentation materials on Pillar Science (TOC in Notes)

- At alternating times to balance time zones and availability

#### 5. Broadening Participation

- Two BP Champions guide SUPREME's efforts

- Two awards established since 2023Q2/Q3

- SUPREME Undergraduate Microelectronics Fellows (7 awarded)

- SUPREME Undergraduate Travel Grant (4 awarded)

- Total number of undergrads working on SUPREME projects: 24

- 6. Publications (on Pillar Science): 130+

- 7. Keynotes: 70+

- 8. Awards: 25+

# **Additional slides**

## **Topics in SUPREME**

- I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- 10. High-throughput materials discovery

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

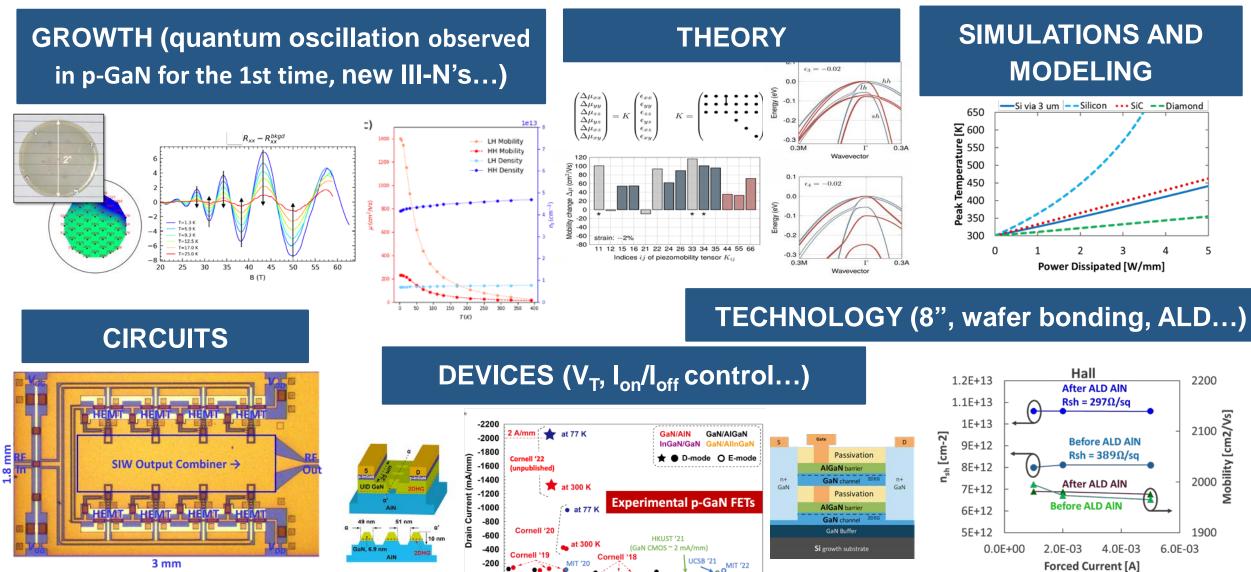

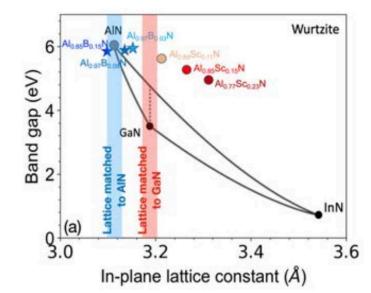

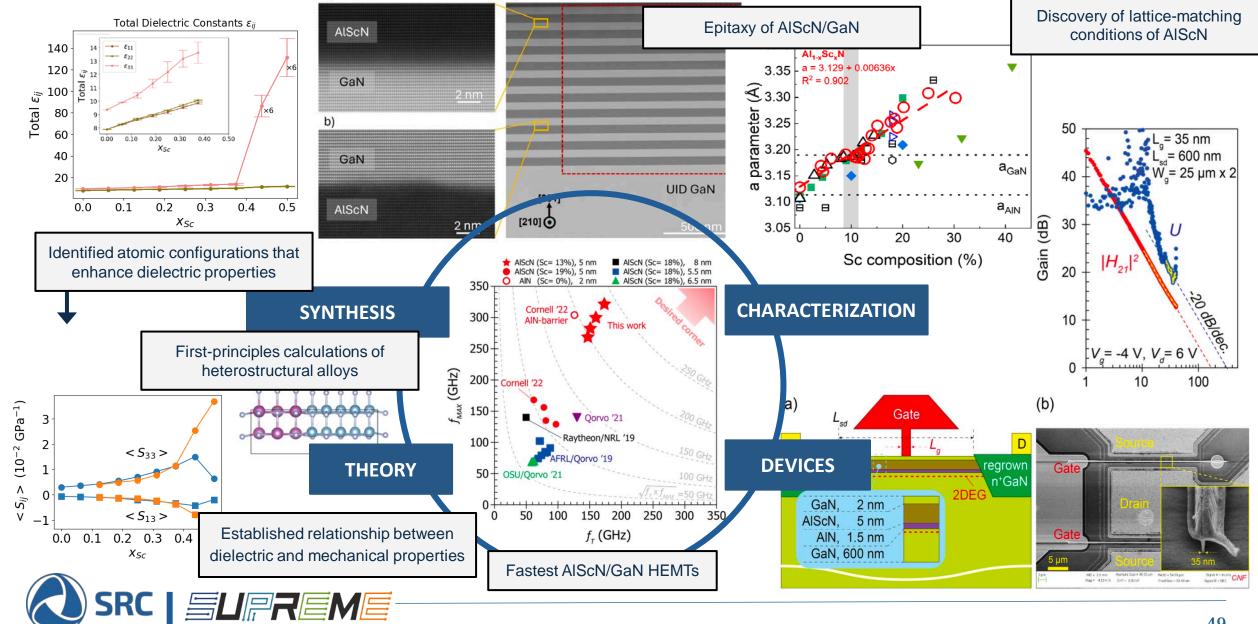

## **Topic: GaN materials and Devices**

- 1. Pls: Debdeep Jena, Grace Xing, Tomas Palacios, James Hwang, Feliciano Giustino

- 2. Tasks: 3137.03/04/05/06/07

- 3. Application: Analog, Power and Mixed Signal

- 4. Objectives:

- a. To develop high-mobility *p*-type GaN channels

- b. To explore sub-THz high-efficiency materials and devices

- c. To develop dual-gate and nano-sheet-based GaN transistors to improve  $V_T$  control and operating frequency.

- d. To explore design space for GaN-on-Si HEMTs to have better performance than GaN-on-SiC

#### 5. SOTA:

- a. p-type RT hole mobility 20-30 cm<sup>2</sup>/Vs

- b. Multi-channel Finfet-like GaN transistors have shown record power densities and efficiencies at W-band (link)

- c. Sub-THz transceivers are large (> $\lambda^2/4$ ) with high noise (>5dB), insufficient power (~0.1W), and low efficiency (~10%)

#### 6. Approaches with feedback loops:

- a. Rational strain engineering via predictive *ab initio* calculations

- b. Strain engineering in practical nanofin devices

- c. AlScN barriers and levering of ferroelectric properties

- d. Design-Technology-Co-Optimization (DTCO) of GaN transistors, assisted by calibrated device-physics s

- e. Development of 8" GaN-on-Si process flow

- f. Silicon substrate removal and wafer bonding for new processing flexibility

- g. 3D heterogeneous integration of GaN chiplets on SiC interposer

## **Topic (achievements): GaN materials and Devices**

10<sup>7</sup>

10<sup>8</sup>

105

1<sub>on</sub> / 1<sub>off</sub>

106

## **Topics in SUPREME**

- I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- 10. High-throughput materials discovery

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

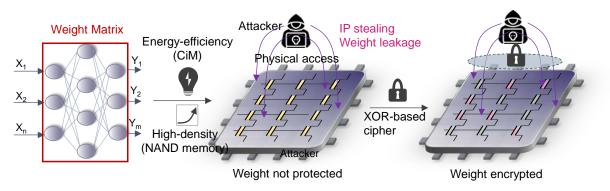

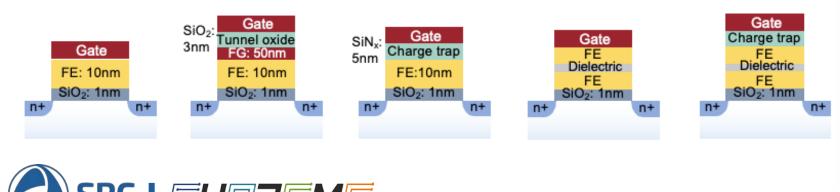

## **Topic: Ferroelectric memories**

- 1. Pls: Asif Khan, Kai Ni, Michael Niemier

- **2. Tasks:** 3137.022, 3137.012, 3137.013, 3137.018

- 3. Application: High-density memory

- 4. Objectives:

- a. To realize ultra-low voltage and high-speed operation of embedded applications

- b. To enable performance augmentation of DRAM and flash technologies using ferroelectric memories

- c. To explore novel architectures and new applications leveraging unique features of ferroelectrics

- 5. SOTA:

- Dual Layer 3-D stacked FRAM, 32 Gb capacity, 450 Mb/mm<sup>2</sup> density, near DRAM performance (Ramaswamy et al. Micron, IEDM 2023).

#### 6. Approaches with feedback loops:

- a. Connecting ferroelectric TEM microstructure with scalability, reliability and variation.

- b. Engineering electrodes and interfacial oxygen reservoirs to control imprint, retention, and endurance in capacitor and FET structures.

- c. ALD approaches to low-voltage perovskite-structure oxides

- d. Benchmarking of different compute architectures and workloads with ferroelectric memories

## **Topic (achievements): Ferroelectric memory and storage**

In-Situ Encrypted FeFET Array for Secure Storage and Compute-in-Memory -Zhao, Ni, et al. IEDM 2023.

Interface design to massively enhance memory window for storage applications.

-Das, Yu, Datta, Khan, et al. IEDM 2023 – Selected as IEDM highlight for memory.

-Collaboration between SUPREME and PRISM PIs and Samsung.

Semiconductor Research Corporation 16,243 followers 3mo • 🚱

X

1 repost

Congratulations to SUPREME Scholar **Dipjyoti Das** and Principal Investigator (PI) **Asif Khan**, PRISM PIs **Shimeng Yu** and **Suman Datta**, and Samsung engineers on this breakthrough!

Read more: https://lnkd.in/gdUtGC5b

🖕 Like 🖙 Comment 🏳 Repost 🛛 🏼 🏹 Send

**Read Article**

**C** You and 38 others

## The Future of Digital Storage

SRC Researchers at GA Tech Collab with Samsung on New Ferroelectric Structure

LinkedIn: https://shorturl.at/iqxBC

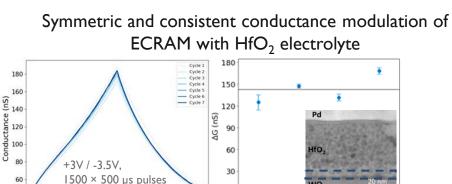

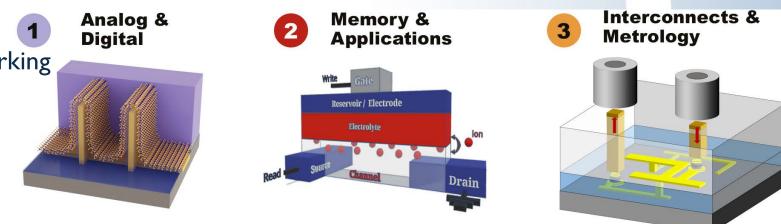

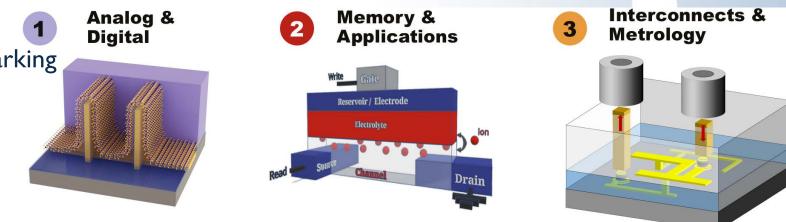

## **Topic: Ionic-Electronic Designer Memories**

- I. PI(s): Bilge Yildiz (MIT), Farnaz Niroui (MIT)

- Collaborating PIs: Jing Kong (MIT), Asif Khan (GaTech), Judy Cha (Cornell), Tomas Palacios (MIT), Kai Ni (Notre Dame), Michael Niemier (Notre Dame)

- **2. Tasks:** 3|37.008, 3|37.0|7

- **3. Application**: Neuromorphic and other unconventional memory and compute applications, AI hardware

- **4. Objective**: Memories with programmable and deterministic conductance characteristics, and fast (ns), energy efficient (aJ) and low voltage (≤IV) modulation

- 5. Approach: I) CMOS-compatible protonic ECRAMs, 2) Devices with transition metal redox-active complexes (TM)

- 6. SOTA: <u>ECRAMs</u> Protonic ECRAMs show 5 ns multistate modulation but require 10 V; ECRAMs based on other ions show μs to ms operation. <u>TM memories</u> Leading examples report multistate behavior and figures of merit competitive to emerging RRAM (<1 V, <30 ns, >10<sup>12</sup> cycles endurance) but limited to μm-scale devices. Limited mechanistic understanding.

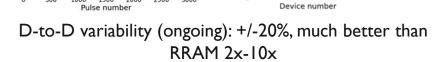

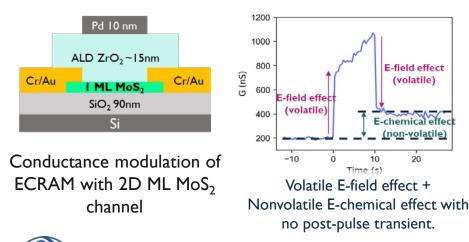

**Recent Accomplishments**: **ECRAMs** – 1) Demonstrated  $HfO_2$  as a CMOS compatible electrolyte in ECRAM. Highk  $HfO_2$  facilitates proton conduction in nano-porous state. 2) Using  $WO_3|HfO_2$  as a model system, we started assessing device-to-device variability, and found it to be much lower than the state-of-the-art RRAMs. This indicates that ECRAM can be more reliable for Al accelerators. 3) Demonstrated  $MoS_2$  and  $V_2O_5$  as a CMOS compatible channel materials, with controllable sensitivity to hydrogen. **TM memories** –1) Designed and synthesized several redox molecules, confirming thermal stability >300°C. 2) Developed a wafer-scale compatible approach to fabricating nanoscale devices based on transition metal molecular complexes. 3) Demonstrated nanoscale devices with stable and repeatable switching behavior (< 1 V and < 200 ns) using a Ru-coordination complex. 4) Developed a correlated in-situ Raman spectroscopy and electrical characterization platform for studying the device working mechanism.

## **Topic (achievements): Ionic-Electronic Designer Memories**

#### ECRAM with CMOS-compatible HfO<sub>2</sub> electrolyte and H-sensitive channels

2

2500

1000

1500

2000

3000

#### TM devices show consistent switching when miniaturized to the nanoscale

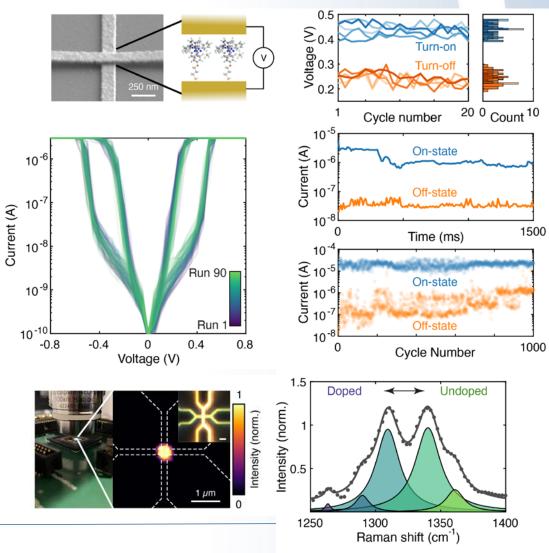

## **Topic: Spintronic materials and devices for logic and memory**

- 1. Pls: Dan Ralph, Luqiao Liu, Farhan Rana, Darrell Schlom, Michael Niemier, James Rondinelli

- **2.** Tasks: 3137.009, 3137.010, 3137.014, 3137.015, 3137.016, 3137.045

- 3. Application: Spin-based logic and memory

- 4. Objectives:

- a. To lower down the writing currents of spintronic device to enable higher density

- b. To increase the read signals for higher memory window

- c. To reduce sensitivity of magnetic information storage element to external magnetic field

- d. To take advantage of unique dynamics of nanomagnets and new topological effects for new computing schemes

#### 5. SOTA:

- a. Weak out-of-plane anti-damping spin-torque efficiency ( $\xi_{DL,z} = 0.014$  from WTe2)

- b. Low Inverse spin Hall Readout from metals for MESO device (Ta V/I = 1.7  $\Omega$ )

- c. Low TMR from MTJ based on antiferromagnet and topological semimetals (TMR ~ 0.1%)

- d. Simple magnetic free layers have coercive fields well below 0.1 Tesla

- e. High sensitivity of probabilistic device to environment, hard to pass true random number generation test.

- 6. Approaches with feedback loops:

- a. Low-symmetry conductors, magnets, and antiferromagnets as spin-source layers

- b. Anomalous Hall effect in topological insulator/magnet structures for high readout signal

- c. Explore antiferromagnetic topological material to achieve high spin polarization

- d. Combine SOT and STT to provide control over the probabilistic switching of nanomagnet

- e. Use intrinsic or synthetic antiferromagnet as the switching component in SOT-MRAM

## Topic (achievements): Spintronic materials and devices for logic and memory

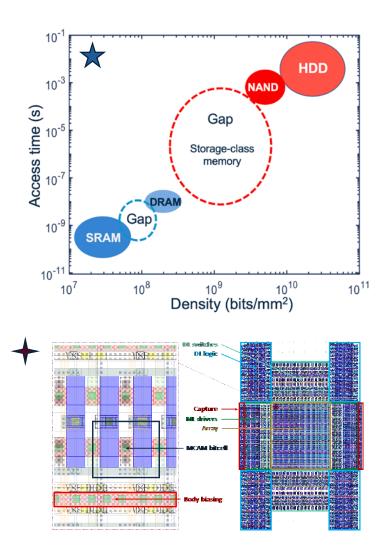

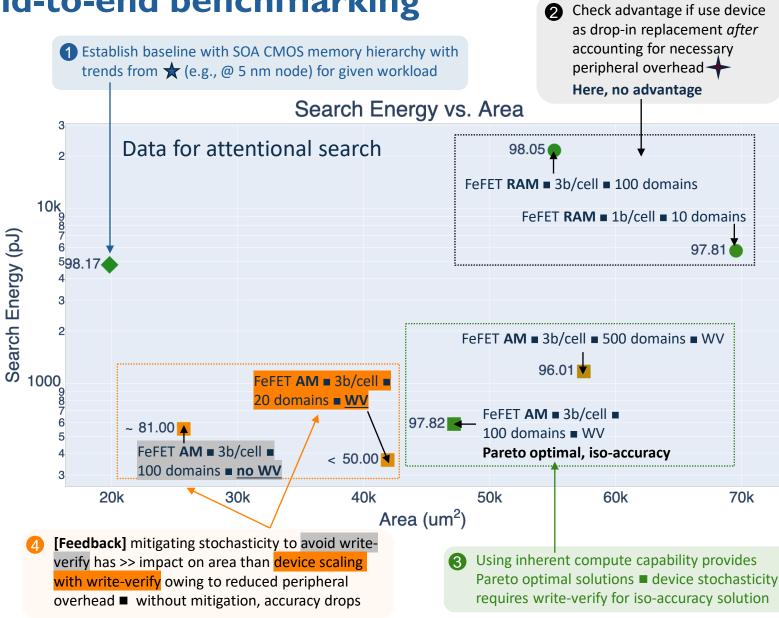

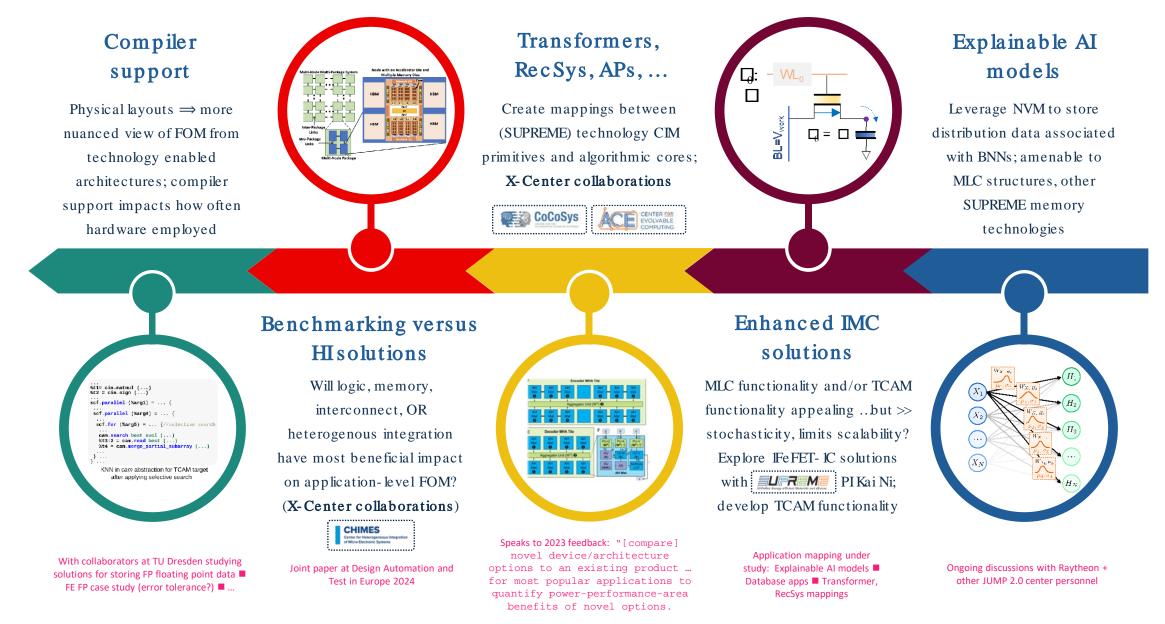

# **Topic: memory benchmarking**

- PIs: Niemier [Khan, Liu, Ni, Niroui, Ralph, Yildiz, SUPREME], [Gupta (CHIMES), Gupta (CoCoSYS), Martínez (ACE), Naeemi (CoCoSYS), Raghunathan (CoCoSYS)]

- **2.** Tasks: 3137.{008,009,011,010,012,013,014,015,016,017,018,027}

- 3. Applications: Device- and materials-driven, application-level benchmarking

- 4. **Objectives:**

- a. Identify value proposition (if any) when SUPREME memory technologies used as drop-in replacement for memory cell {SRAM, DRAM, Flash, ...} in existing memory hierarchy

- b. Identify value proposition (if any) for technology-enabled compute-in-memory architecture that exploits SUPREME memory technology in context of application-level workload (ideally identified by vertical JUMP 2.0 centers)

- c. Identify impact of necessary peripherals for options (1) and (2) + how (at scale) peripherals impact application-level FOM

- d. Identify {materials, device} design levers that maximize improvements to application-level FOM

## 5. **SOTA**:

- a. Established architectural solutions (e.g., GPU, TPU, HBM @ advanced technology node)

- b. In-memory prototypes from academic, industrial collaborators

## 6. Approaches with feedback loops:

- a. Highly-scaled memory devices as drop-in replacement for traditional memory hierarchy (possibly multi-bit storage)

- b. Highly-scaled memory devices used in in-memory computing architecture (with nominal compute functionality); key compute kernels workloads informed by vertical center research

- c. Layout-based analysis at advanced technology nodes to identify optimal paths at materials, device-levels to derive application-level benefits

# **Topic (achievements): End-to-end benchmarking**

# **Topics in SUPREME**

- I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- 10. High-throughput materials discovery

- II. Advanced processing

- 12. High-k dielectrics & ferroelectrics

Materials Discovery & Processing: Taming new materials and new physics.

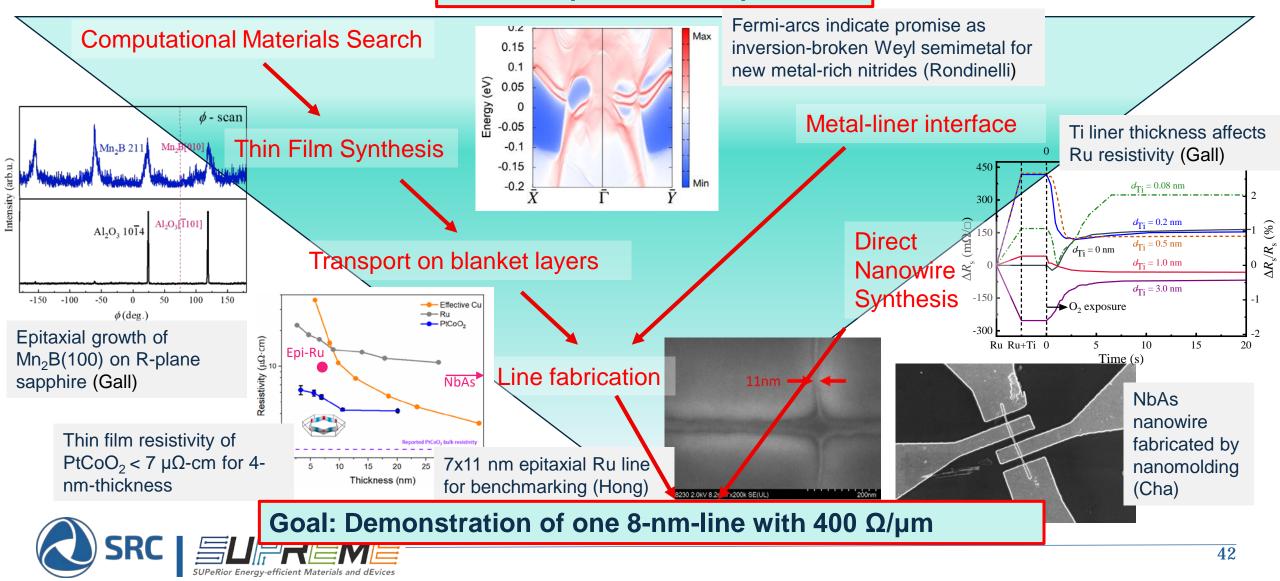

# **Topic: Materials for high-conductivity interconnects**

- 1. Pls: Daniel Gall, Judy Cha, Christopher Hinkle, Hong Tang, James Rondinelli

- 2. Tasks: 3137.019, 3137.020, 3137.021, 3137.026, 3137.038, 3137.046

- 3. Application: High-conductivity narrow interconnects

- 4. Objectives:

- a. To identify materials with high conductivity at small < 10 nm dimension

- b. To develop thin film synthesis methods including control of composition and crystalline direction

- c. To develop nanowire fabrication processes

- d. To demonstrate high-conductivity narrow wires with < 400  $\Omega/\mu$ m for 8 nm line width

- 5. SOTA:

- a. Cu with Ta/TaN or Co liner: 4,000  $\Omega/\mu m$  (extrapolated to 8 nm line)

- b. Co with Ti(N/C) liner: 2,000 (extrapolated to 8 nm line)

- c. Ru: 800  $\Omega/\mu m$  (imec 2024, 9 nm line)

#### 6. Approaches with feedback loops:

- a. First-principles computational search for new topological conductors (Rondinelli)

- b. High-throughput thin film materials synthesis (Hinkle)

- c. In-situ transport on epitaxial layers for resistivity benchmark (Gall)

- d. Direct high-throughput wire synthesis through nanomolding (Cha)

- e. Top-down lithography for <10-nm-line fabrication and transport measurements (Hong)

## **Topic (achievements): Material down-selection for interconnects**

#### Start: 10<sup>6</sup> possible compounds

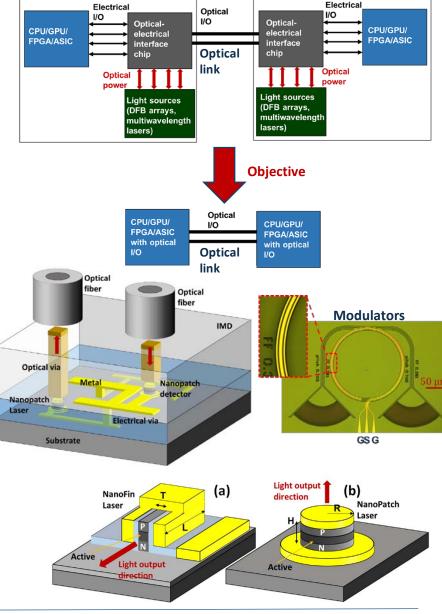

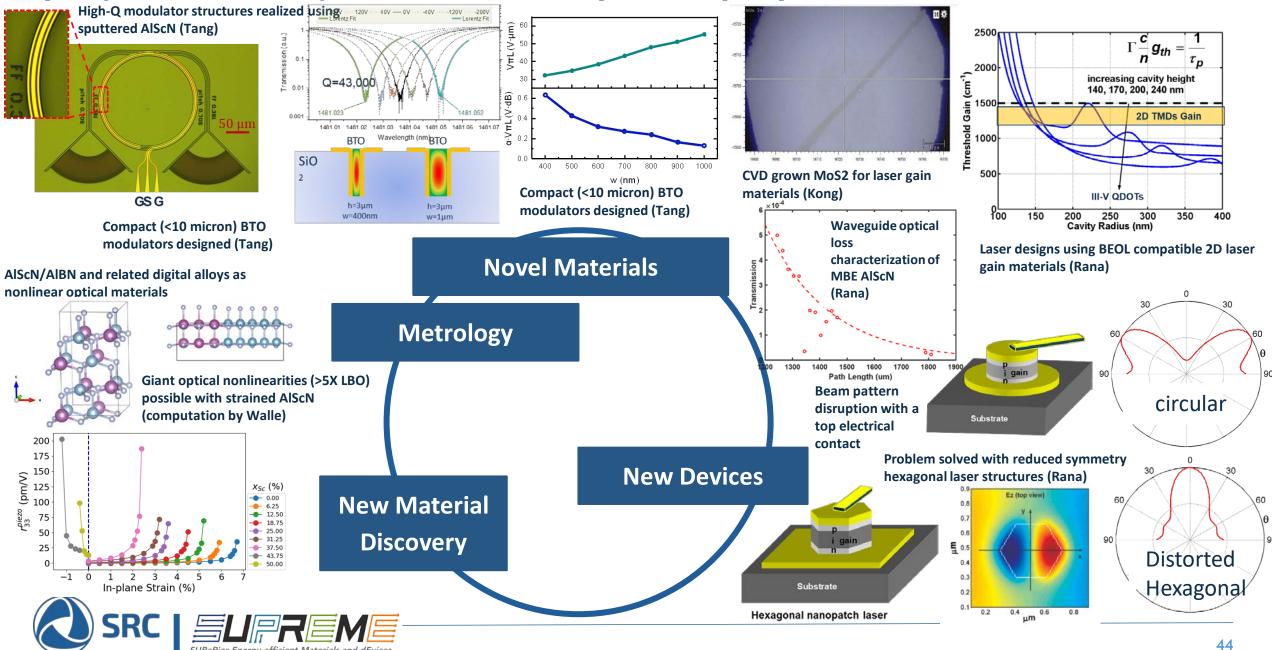

## **Topic: Materials and Devices for Chip-to-Chip Optical Interconnects**

- 1. PIs: Hong Tang, Chris G. Van de Walle, Debdeep Jena, Farhan Rana

- 2. Tasks: 3137.023, 3137.022, 3137.034

- 3. Application: Power and size efficient chip to chip optical interconnects

- 4. Objectives:

- a. Development of new materials and devices for optical interconnects

- b. Reduce the size and power consumption of optical components for interconnects

- c. Develop compact broadband optical modulators for BEOL placement

- d. Develop nanoscale directly-modulated optical light sources for BEOL placement

- 5. SOTA:

- a. Light sources and modulators are placed off-chip increasing system size and complexity

- b. Compact modulators are not broadband and require exacting temperature stabilization (<0.5°K variation tolerable)</li>

- c. Light sources have large footprints and power consumptions, and slow direct modulatice speeds (typically <40 GHz)

- d. Most optical materials are not BEOL compatible

- 6. Approaches with feedback loops:

- a. Development of new highly nonlinear materials (>5X of LBO) for optical modulators

- b. Development of nanoscale, high-modulation bandwidth (>150 GHz), light sources

- c. Explore BEOL compatible materials

- d. Discover new materials and device structures via computational studies, metrology, and characterization

### **Topic (Achievements): Materials for Chip-to-Chip Optical Interconnects**

# **Topics in SUPREME**

- I. 2D materials & devices

- 2. Nitride materials & devices

- 3. Oxide materials & devices

- 4. Ferroelectric memories & benchmarking

- 5. Spintronic materials & devices

- 6. Ionic materials & devices

- 7. Electrical interconnects

- 8. Optical interconnects

- 9. Metrology

- 10. High-throughput materials discovery

- II. Advanced processing

- **12. High-k dielectrics & ferroelectrics**

Materials Discovery & Processing: Taming new materials and new physics.

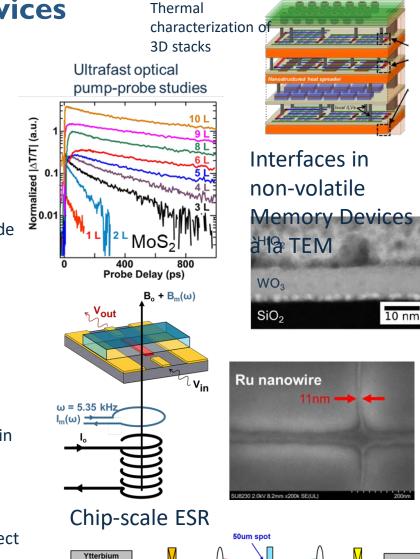

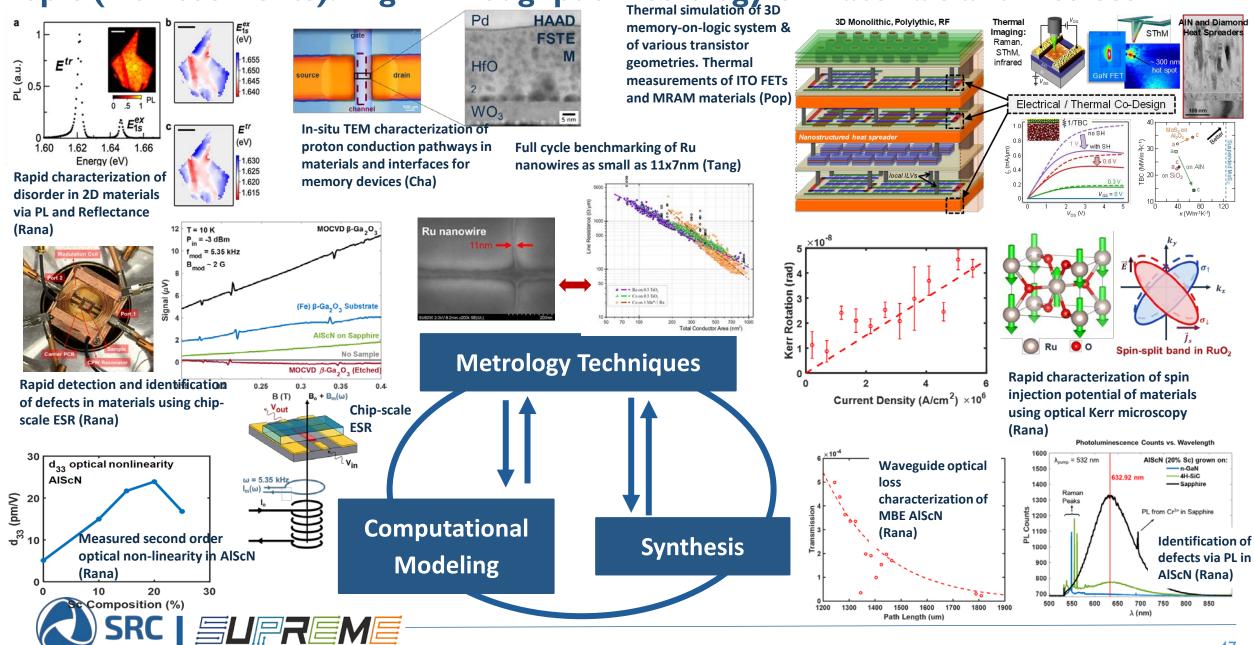

## **Topic: High-Throughput Metrology of Materials and Devices**

- 1. Pls: Hong Tang, Daniel Gall, Eric Pop, Chris Hinkle, Elton Graugnard, Judy Cha, Farhan Rana

- 2. Tasks: 3137.026, 3137.044, 3137.025, 3137.024

- 3. Applications: Develop rapid techniques for material and device characterization

- 4. Objectives:

- a. Measure and characterize the properties of materials being developed in the center

- b. Develop techniques for the high-throughput characterization of materials and devices and provide feedback to material synthesis and computational modeling teams in the center

- c. Develop characterization techniques for rapid material discovery via machine learning

- 5. SOTA:

- a. Most material characterization techniques require full device fabrication to access material properties and are not suitable for rapid material characterization

- 6. Approaches with feedback loops:

- a. Use optical, IR, and Terahertz techniques for material characterization

- b. Use chip-scale electron spin resonance technique for the detection and identification of defects in thin films and at material interfaces

- c. Use in-situ TEM techniques to characterize materials and devices

- d. Use Raman, SThM, and electrical techniques for studying material thermal properties

- e. Develop automated schemes for the electrical characterization of nanoscale electrical interconnect materials

Laser (1032nm)

Polarize

Analyze

(Controlled sample tilt

3D Monolithic, Polvlythic, R

## Topic (Achievements): High-Throughput Metrology of Materials and Devices

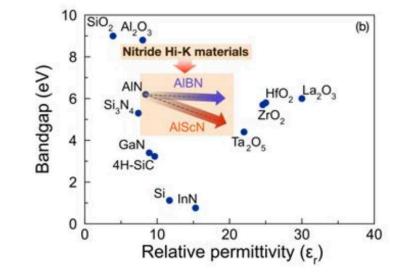

## **Topic: Next-generation ferroelectrics and high-K dielectrics**

- I. PIs: Depdeep Jena, Farhan Rana, Hong Tang, Asif Khan, H. Grace Xing, Elton Graugnard, Chris G. Van de Walle

- **2. Tasks:** 3 | 37.004, 3 | 37.034, 3 | 37.035

- **3. Application**: Wide-bandgap transistors for high-efficiency gate drivers, RF and logic/memory hybrids

- **4. Objectives**: Discovery of new high-K dielectric and ferroelectric barriers for wide-bandgap CMOS devices and circuits

- **5. SOTA**: AlScN/GaN FerroHEMTs with  $f_{max}$ =150 GHz and 2 A/mm on currents, I V memory window

#### 6. Approaches with feedback loops:

- 1. First-principles calculations of AIScN, identification of microscopic structures responsible for enhancements/switching

- 2. Experimental synthesis (epitaxy) and characterization; correlation with calculations

- 3. Fabrication and characterization of nitride high-K/ferroelectric gated GaN HEMTs grown on full wafers

- 4. Computational and experimental exploration of the AIScN barrier material space

- 5. Build on insights to explore and find opportunities for other novel systems: AIBN,AIYN,AILaN

## Topic (achievements): Next-generation ferroelectrics and high-K dielectrics

## **Example collaborations**

Seed projects under evaluation:

- SUPREME PRISM

- SUPREME CHIMES

- SUPREME CUBiC

- SUPREME CoCoSys

### Intra-, Inter-center + industrial collaborations (memory benchmarking)

51

# **SUPeRior Energy-efficient Materials and dEvices**

Grace Huili Xing (Cornell), Center Director Tomás Palacios (MIT), Co-Director Chris Hinkle (ND), co-Lead on High-Throughput Elton Graugnard (BSU), Thrust Lead on Advanced Processing Thomas Dienel (Cornell) Managing Director, Jenna LaMendola (Cornell) Administrative Assistant