# Global Research Collaboration (GRC) and Calls for Research

# Meet the GRC Research Management Team

John Oakley Science Director for AIHW, HWS, PKG, SCARF john.oakley@src.org

Kashyap Yellai Science Director for ESH, LMD, NMP <u>Kashyap.yellai@src.org</u>

Marcus Pan Science Director for AMS-CSD, CADT <u>marcus.pan@src.org</u>

LaDonya Dooley Program Coordinator laDonya.dooley@src.org

Sydney "Syd" Williams-Black Program Coordinator Syd.Williams-Black@src.org

LaTanya Holmes Program Coordinator latnya.holmes@src.org

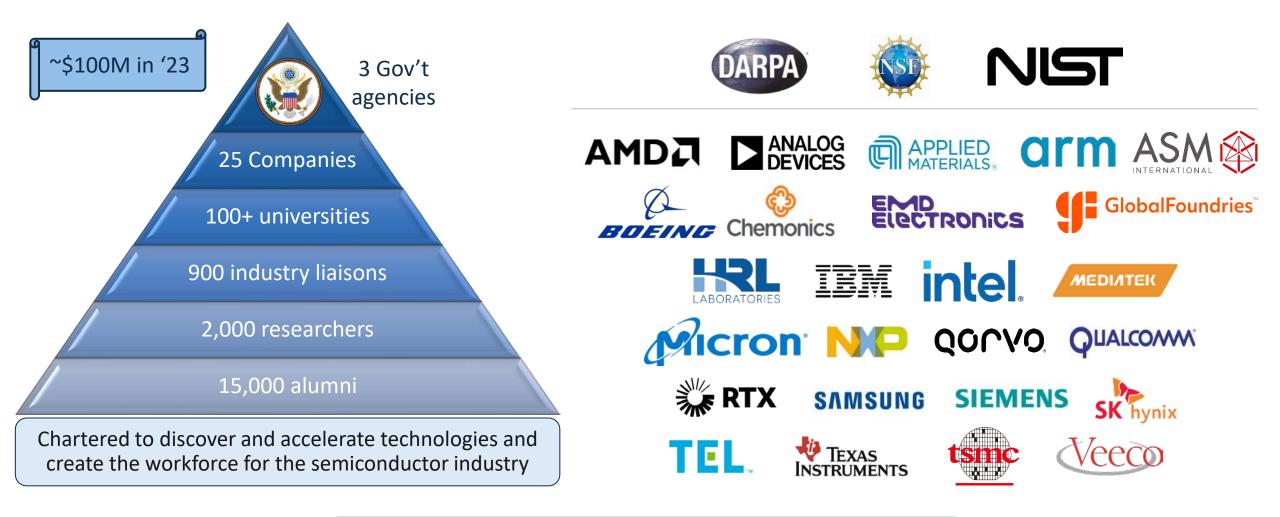

### Who We Are: Premier Global Microelectronics Consortium

Members are large companies across the supply chain

#### https://www.src.org/src/member/roster/

SRC

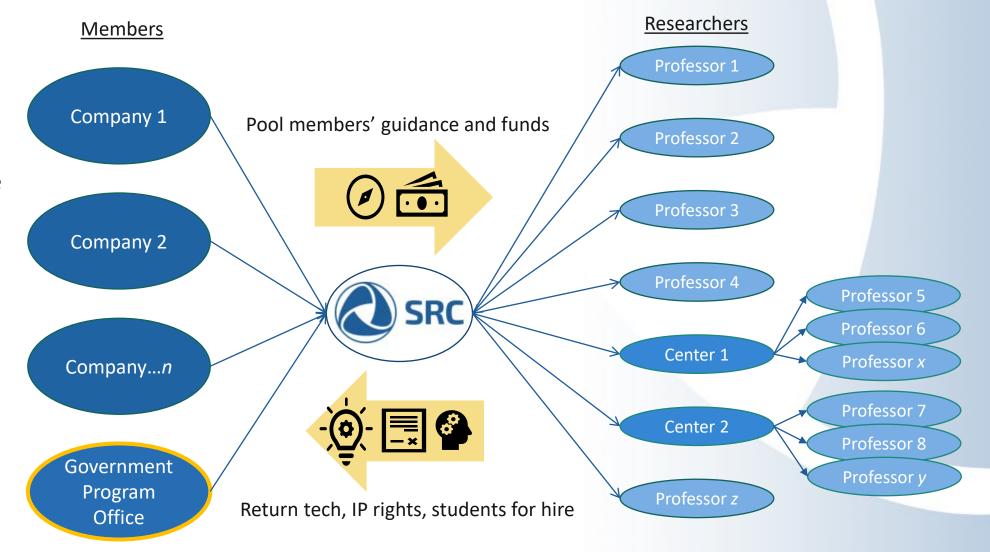

# What We Do: Manage Collaborative R&D Programs

SRC manages research programs on behalf of members;

- Recruit members

- Run solicitations

- Manage performance

- Ensures tech transfer to members

In-house Contracting, Legal, Event Production, Billing, MarCom, web portal, etc.

SRC members jointly define research needs, fund selected projects, and reap the rewards PI will directly engage with experts and conduct research relevant to industry applications

## **Evidence of Success: 40+ Years of Technology & Workforce**

#### **Historic Model**

\$2.2B of collaborative research

700+ patents issued from 2,000 research projects

15,000 SRC sponsored students at 250 universities globally

#### **Providing critical technology**

- Nanosheets for GAA transistors

- FinFET

- High K Dielectrics

- Cu interconnect

- MRAM

- Scalable FLASH Memory

- Simulation, verification tools

- CMOS mm wave circuit design

- Quality and cost of testing

- Many more!

Chartered to discover and defining the future's technologies and create the workforce critical for the success of semiconductor industry

# **Industry and Academia Collaboration**

### After Winning a SRC Research Contract: SRC Intellectual Property Requirements

SRC desires to protect intellectual property rights vesting in you and your University emanating from sponsored research. In return for sponsoring the research, SRC receives certain Intellectual Property (IP) rights. The primary goal of <u>SRC's IP policy</u> is to provide Members and Participants freedom to practice results of the sponsored research. SRC's Science Directors and industry representatives assist researchers in the identification of inventions that may be formally protected.

The sponsored research agreement (SRA) provides for IP license rights, which are sublicensed to Members and Participants. The license grant is worldwide, non-exclusive, non-transferrable, royalty free and includes the right to make, have made, use, or sell inventions, and to prepare software derivative works. In addition, SRC retains an option to negotiate an exclusive license. The University retains ownership of the IP and is free to license the IP to companies that are not SRC Members or Participants, subject to SRC's option for an exclusive license.

This license includes all IP that can be protected by patent, copyright, or other form of protection, including inventions, works of authorship, and mask works.

### Value in Engagement of Academia and Industry Liaison

Innovation

Workforce

Highlights technological challenges in the domain

Industry

Liaison

Provides direction on the relevance of research

Provide an out of the box approach and diversity in perspective to address challenges

Academia

Enhance industry R&D that enables a differentiated product for the marketplace

## **Researcher Own Industry Interactions**

- Setup Regular Liaison Calls & Student Participation

- Requires researcher-liaison calls every 4 to 8 weeks for GRC projects.

- The university researchers own the interaction format and frequency of these meetings based on the feedback from the liaisons

Project leader should encourage students to present results in these meetings

### **Resources that Help Academics Evaluate, Adopt, and Amplify Emerging Member Solutions**

### Member Resources

- SRC has collected information members provide for the academic community, including education, design, and prototyping

- SRC researchers and students are encouraged to take advantage of these resources in their research and education activities

- Link to the resources: https://www.src.org/program/grc/guide/researcher/guidelines/

INFORMATION

About SRC

Privacy Policy Members & Partners

Contracts & IP Management Charts

Corporate Annual Reports

News.

FAQs

Contact

SRC VALUE Awards Programs Patents Recruiter Guide SRC Timeline

LSAC

ACADEMIA Researcher Resources Funding Opportunities Career Opportunities Participating Universities Education Alliance

#### Member Resources

SRC has collected information members provide for the academic community, including education, desig prototyping. SRC researchers and students are encouraged to take advantage of these resources in their education activities

Intel

- Intel Open Data Center Diagnostic Project

- Intel Academic Compute Resource Environment (ACE)

- Intel Academic Program for oneAPI

- Analog Devices

- Active Learning Program

- ADALM-SR1 Hardware

- ADALM-SR1 Switching Regulator Active Learning Module

ARM

ARM Academic Access ARM Education

- ARM University Program Education Kits

- ARM Education Online Courses

- ARM Education Textbooks and Reference Books

Texas Instruments Specific tutorial and curriculum for universities include:

- Texas Instruments University Program

- TI Robotics System Learning Kit

- TI Power Management Lab Kit

- TI Experimental Power Electronics Reference and Curriculum

- TI Precision Labs

IRM

- IBM tutorial and curriculum for universities

- IBM Skills Academy

- IBM + Coursera

- IBM PhD Fellowship Program

- IBM Quantum Computing student opportunities

- IBM AI Hardware

NXP

Rapid IoT Prototyping Kit

Siemens

EDA Academic Products

Oualcomm

University Relations Program

SRC Select Disclosure 10

4819 Emperor Blvd, Suite 300 Durham, NC 27703

FOR MEMBERS

Lalsons

My Company @ SRC

Voice: (919) 941-9400 Fax: (919) 941-9450

# Highlighting Relevant Technology Transfers from Researchers

### 2023 - 1H: Technology & Workforce Development Highlights

#### January: Auto

Michigan State Univ: Development of multi-level and detection framework,...for autonomous vehicles

Prof. Hayder Radha, Prof: Su Pang

#### April: CADT

Univ of Arizona: Diversity Vehicles Prof. Sule Zev

February: ComSenter + ASCENT Georgia Tech: World's 1st Embedded Die with D-Band Integrated Antenna in a Glass Interposer Transferred to SHIP

Prof. Madhavan Swaminathan

Univ of Washington. Level of Detail (LoD),

Talent Transfer

Prof. Zachary Tatloc., Dr. Bill Zorn

Mav: ADA

March: nCORE, Nev s Stanford Univ: Sele Diversity 2D TMD Ma Prof. Star ent

https://www.src.org/newsroom/newsletter/

June: Artificial Intellig ce HW Univ of Californic Hyperdimensic Young (HDC), Your Faculty

Prof: Mo<sup>y</sup>en Imani

### 2023 - 2H: Technology & Workforce Development Highlights

# **GRC Research Programs**

### GRC Programs Solicitation for Research is Described and Guided by

#### Five Seismic Shifts Described in Decadal Plan for Semiconductors

- 1. Fundamental breakthroughs in analog hardware are required to generate smarter world-machine interfaces that can sense, perceive, and reason. Investment throughout this decade to pursue analog-to-information compression/reduction with a practical compression/reduction ratio of 10<sup>5</sup>:1 for practical use of information more analogous to the human brain.

- Memory & Storage

- 2. The growth of memory demands will outstrip global silicon supply, presenting opportunities for radically new memory and storage solutions. Investment throughout this decade to develop emerging memories/memory fabrics with >10-100X density and energy efficiency improvement for each level of the memory hierarchy. Discover new storage systems and storage technologies with >100x storage density capability.

- **B.** Always-available communication requires new research directions that address the imbalance of communication capacity vs. datageneration rates. Investment throughout this decade for communication enabling data movement of 100-1000 zettabyte/year at the peak rate of 1Tbps@ <0.1nJ/bit. Develop intelligent and agile networks that effectively utilize bandwidth to maximize network capacity.

- 4. Breakthroughs in hardware research are needed to address emerging security challenges in highly interconnected systems and AI. Investment throughout this decade for privacy and security hardware advances that keep pace with new technology threats and use cases (e.g., trustworthy AI systems, secure hardware platforms, and emerging postquantum and distributed cryptographic algorithms).

Security

Communication

5. Ever-rising energy demand for computing vs. global energy production is creating new risk, and new computing paradigms offer opportunities to dramatically improve energy efficiency. Investment throughout this decade to discover computing paradigms/architectures with a radically new computing trajectory demonstrating >1,000,000x improvement in energy efficiency.

#### 11 Chapters in MAPT Roadmap

#### https://www.src.org/about/decadal-plan/

https://srcmapt.org/wp-content/uploads/2024/01/SRC-MAPT-Roadmap-2023-v2.pdf

### Global Research Collaboration (GRC) Research Programs

| Logic and Memory Devices        | Defining the future of transistor technology including exploration of augmenting the advanced CMOS technology with emerging alternative concepts such as multiferroics, spintronics, photonics, and 3D integration.     |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al Hardware                     | Pushing the frontiers of artificial intelligence across a broad spectrum of applications from the edge to the cloud.                                                                                                    |

| Packaging Technology            | Spanning from small, flexible, mobile interconnected consumer devices to cloud based computing requiring high compute density in data centers.                                                                          |

| Hardware Security               | Developing strategies, techniques, and tools to provide assurance that electronic systems will perform as intended. Assurance depends on processes and tools across all steps of design, manufacture, and distribution. |

| Nano Materials and<br>Processes | New materials and processes for scaling digital and analog device fabrication. Addresses challenges in patterning, nanoengineered materials, deposition/ etch processes, process integration, metrology, and ESH.       |

| Analog/Mixed-signal<br>Circuits | Creating fundamental innovations in integrated circuits and systems that improve energy efficiency, health care, public safety, and security.                                                                           |

| CAD and Test                    | Leading electronic design automation techniques, and tools for the design and test of advanced electronic circuits and systems.                                                                                         |

| Environment Safety &<br>Health  | Develop sustainable and environmentally benign processes for semiconductor manufacturing.                                                                                                                               |

## **GRC Upcoming Solicitations**

Welcome to the SRC OpenWater portal

### Semiconductor Research Corporation 2024 Call for Research

| Research Thrust                           | Call<br>Opens | Papers<br>Due      | Program Manager | Program Coordinator |

|-------------------------------------------|---------------|--------------------|-----------------|---------------------|

| Nanomanufacturing Materials and Processes | Apr 9         | May 7              | Kashyap Yellai  | Syd Williams-Black  |

| Packaging / Packaging Chirp               | Apr 9         | May 7              | John Oakley     | LaDonya Dooley      |

| Hardware Security                         | May 7         | Jun 4              | John Oakley     | LaDonya Dooley      |

| Computer-Aided Design and Test            | May 7         | Jun <mark>4</mark> | Marcus Pan      | LaTanya Holmes      |

| Environment, Safety, and Health           | May 7         | Jun 4              | Kashyap Yellai  | Syd Williams-Black  |

- Each program runs solicitation every 2 out of 3 years

- 2024 solicitations (1/1/2025 start) will create new research for CADT, ESH, HWS, NMP, and PKG

- The 2024 solicitations use a \$105k/yr to \$135k/yr. for three years starting 1-Jan-25 starts

### Hardware Security Research Program Overview

#### Program Objective:

Developing strategies, techniques, and tools to provide assurance that electronic systems will perform as intended. Such assurance is a function of processes and tools integrated across design, architecture, manufacturing, and distribution.

Size:Steady state annual budget >\$1.5M/year supporting 17 current research tasks

Members: • AMD, Analog Devices, IBM, Intel, Siemens EDA, Texas Instruments

| Call<br>Opening<br>May 7                                          |                    | Trusted Architectures and Hardware Security                     |

|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------|

| HWS Metrics                                                       |                    | Security Techniques for Advance Technologies and Packaging      |

| Current<br>17 Projects<br>13 Universities<br>40 Research Scholars | Research<br>topics | Security Aspects of Embedded Software,<br>Firmware, and Soft IP |

| 21 Faculty Researchers<br>40 Liaisons                             |                    | Security Assurance, Protection, and Verification                |

|                                                                   |                    | Authentication, Attestation, and Provisioning                   |

#### https://www.src.org/program/grc/hws/

HWS

### Packaging Research Program Overview

#### Program Objective:

Create and explore advanced evolutionary and revolutionary packaging technologies for reliably encapsulating and efficiently integrating microsystems

#### Size:

# Steady state annual budget at \$2.7M/year supporting 40 current research projects CHIRP has significant cost sharing with 1:1 matching from universities for 13 projects

• IBM, Intel, MediaTek, NXP, Samsung, SK

hynix, Texas Instruments

Call Opening April 9

#### **PKG Metrics**

#### Current

38 Projects 23 Universities

128 Research Scholars

50 Faculty Researchers

117 Liaisons

**Design Enablement and Tools**

#### Interconnects including photonics

Power Delivery and Thermal Management

Metrology and Modeling

Materials

Research

topics

Heterogeneous Integration (HI)

#### PKG

# **Pilot Program for Seed Grants**

| Proposal | <ul> <li>\$25k grants (gifts) for 1yr for exploratory ideas</li> <li>Grants have no IP rights and minimal deliverables (only optional final report)</li> <li>And no university overhead (dollars go farther)</li> <li>Successful seeds could migrate to full 2-year projects on next solicitation with normal project parameters</li> </ul> |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Criteria | <ul> <li>Research thrust must:</li> <li>Have greater than \$1M solicitation</li> <li>Currently AMD-CSD, LMD, NMP, PKG and AIHW are eligible</li> <li>Be in year 1 of back-to-back solicitation years</li> </ul>                                                                                                                             |

|          |                                                                                                                                                                                                                                                                                                                                             |

| Pilot    | <ul> <li>2024 Solicitation in Packaging will have 6 seed grants</li> </ul>                                                                                                                                                                                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                                                             |

| SRC —    |                                                                                                                                                                                                                                                                                                                                             |

|          | SRC Select Disclosure 20                                                                                                                                                                                                                                                                                                                    |

# Computer Aided Design and Test (CADT) Program

#### **Program Objective**

Provides research leadership in electronic design automation by making available to members leading-edge university research results, techniques, and tools for the design and test of advanced electronic circuits and systems.

Size

### Steady state annual budget of \$1.47M supporting 26 current research tasks

<u>Members</u> IBM, Intel, Siemens EDA, Texas Instruments Call Opening May 7

#### **CADT Metrics**

#### Current

25 Projects 16 Universities 54 Research Scholars 26 Faculty Researchers 81 Liaisons

|                                                | 0                                                                                        |

|------------------------------------------------|------------------------------------------------------------------------------------------|

| Research Topics                                | Subsection                                                                               |

| Functional Safety<br>Tools and<br>Techniques   | F1. Safe System                                                                          |

|                                                | F2. Data Mining and Failure Prediction                                                   |

|                                                | F3. Design for Functional Safety                                                         |

| System, Logics and<br>Physical Design<br>Tools | S1. System Tools                                                                         |

|                                                | S2. Tools for Design Robustness                                                          |

|                                                | S3. Analog Tools                                                                         |

|                                                | T1. Test of Machine Learning Systems                                                     |

| Tast Viold and Past                            | T2. Test Cost Quality and Yield Improvement                                              |

| Test, Yield and Post-<br>Silicon Validation    | T3. High Level Test, Validation, Diagnosis and Repair                                    |

|                                                | T4. Analog, Mixed Signal, RF, High-Speed Test                                            |

|                                                | V1. Verification for Machine-Learning Systems                                            |

| Verification                                   | V2. Machine Learning Techniques for Verification                                         |

|                                                | V3. System-Level Verification                                                            |

|                                                | N1. Raise Level of Abstraction in HW design as a continuation of SW development          |

| New Frontier for<br>Scalable,                  | N2. Design Implementation through Trusted<br>Complier/Behavior Synthesis Transformations |

| Correctness-Assured<br>Hardware Design         | N3. Provably Correct Design Construction                                                 |

|                                                | N4. Verification as an integral part of Design Evolution                                 |

https://www.src.org/program/grc/cadt/

CADT

### Environment, Safety and Health Research Program Update ESH

#### Program Objective:

Supports an overall mission of enabling the development of more environmentally preferable processes used in integratedcircuit manufacturing

Size: Stead \$1.4 resea

Steady state annual budget of \$1.49M supporting 13 current research tasks

Members: EMD Electronics, Global Foundries, IBM, Intel, Micron, Texas Instruments Call Opening May 7

#### ESH Metrics

#### Current

13 Projects

8 Universities

29 Research Scholars

20 Faculty Researchers

53 Liaisons

PFAS

Characterization in FAB

wastewater

- Treatment methods

- Hazard and toxicity assessment

Environmentally Preferable HFC etchants and CMP slurries

Assessment of energetics in exhaust and control mechanisms

#### Abatement of NO2 and NOx

https://www.src.org/program/grc/esh/

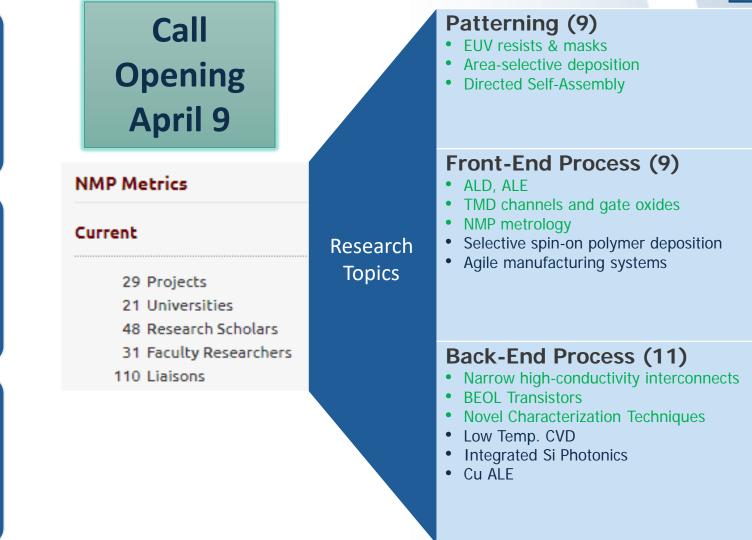

### Nanomanufacturing Materials and Processes Research Program

#### Program Objective:

Explores new materials and processes for scaled digital and analog device fabrication

Size: • Ste \$2. res

Steady state annual budget of \$2.3M supporting 30 current research tasks

Members

ASM, IBM, Intel, Samsung, Siemens, SK Hynix, TEL, TSMC, Veeco

https://www.src.org/program/grc/nmp/

NMP

# Helpful Suggestions for Submitting to the Call

- I. Read and review SRC's MAPT Roadmap (<u>https://srcmapt.org/</u>) as these will be referenced in the upcoming calls for research

- 2. White Papers or Proposals will standout if anticipated results from research can be benchmarked against the State of the Art

- 3. Leverage our pilot program of seed grant (packaging this year) to gain visibility for your research with industry sponsors

- 4. Build upon member resources to improve impact

- 5. Have clear deliverables planned over the project (at least I per year)

- Can be adjusted later with agreement of Program Manager and liaisons

- 6. Consider collaborating with larger universities to improve white papers

- 7. Submit white papers, proposals, and future deliverables on time 🙂