Request for Proposals for the nanoelectronic COmputing REsearch (nCORE) Program

- A. Background

- A1. Research Areas of Interest

- A2. Proposal Process

- A3. Program Scope and Planned Funding Level

- B. Proposal Guidelines and Schedules

- B1. Purpose, Format, Content and Length of Solicited Proposals

- B2. Proposal Submission Process and Related Information

- B3. Evaluation Criteria and Selection and Award Process

- B4. Solicitation Schedule

A. Background

The SRCco Inc. (“SRCco”) is soliciting proposals from U.S. universities qualified to do research in areas of interest to the nanoelectronic COmputing REsearch (nCORE) program. SRCco makes this solicitation in connection with and as part of the nCORE program and nCORE’s collaboration with the National Institute for Standards and Technology (NIST). nCORE participants currently consist of ten leading semiconductor, electronics, and defense companies: IBM Corporation, Northrop Grumman Corporation, Micron Technology, Inc., Intel Corporation, EMD Performance Materials (a Merck KGaA affiliate), Analog Devices Inc., Raytheon Company, Taiwan Semiconductor Manufacturing Company Ltd., Lockheed Martin Corporation and Samsung Electronics Co., Ltd.

SRCco, a not-for-profit research management organization, is a wholly-owned subsidiary of the Semiconductor Research Corporation (SRC). SRC is a research management consortium that was established in 1982 and sponsors semiconductor research.

Semiconductors are the foundation of information and communication technology (ICT), consumer electronics, online business, and social media. Advances in semiconductor technology are critical for the economic prosperity, employment, and national security of the U.S. For over half a century, dimensional scaling of the field-effect-transistor (FET) in complementary metal oxide semiconductor (CMOS) technology has been the innovation engine behind the over $300 billion global semiconductor industry. As the industry approaches the fundamental limit of CMOS scaling, there is a critical need to develop novel computing technologies beyond CMOS.

The nCORE program is funded by leading semiconductor companies to support collaborative university research in the U.S. to develop key technologies to enable novel computing and storage paradigms with long-term impact on the semiconductor, electronics, computing, and defense industries. It is driven by fundamental research on emerging materials and devices with the potential to achieve significantly improved efficiency, enhanced performance, and new functionalities, beyond the capability of conventional CMOS technologies. nCORE is a new program built upon the Nanoelectronics Research Initiative (NRI) (www.src.org/program/nri/). NIST has provided deep technical expertise and substantial financial support for the NRI program. Nanoelectronics research requires innovative metrology and characterization technology; therefore, NIST is a critical partner for the semiconductor industry in the nCORE program.

The NRI research has explored a broad spectrum of beyond-CMOS devices for a “new logic switch” to replace the current CMOS-based transistor. While NRI has significantly advanced basic device and material research, a “better switch” has not been found. Comprehensive benchmarking of beyond-CMOS devices by NRI researchers has revealed little or no advantage of these devices over CMOS for conventional Boolean logic and the von Neumann architecture; however, some devices demonstrate unique characteristics suitable for novel architectures or computing paradigms, e.g., nonvolatility in logic devices, reconfigurability, high computation density. Thus, a critical lesson from NRI is the importance of co-optimization of novel devices and architectures to maximize system performance. At the same time, the ICT industry is experiencing a significant shift from conventional computing models, algorithms, and applications to novel computing and storage paradigms. Although some of these novel paradigms will be implemented first with CMOS technology, more efficient and fully functional implementations will require new hardware platforms beyond the capabilities of conventional CMOS technology. Sustainable and scalable innovations in computing technology need to originate from basic material and device research. Built upon the NRI research, nCORE will focus on utilizing unique characteristics of emerging materials and devices to optimize novel architectures that achieve efficiency and performance significantly beyond the theoretical limits of CMOS. The program will also fund innovative metrology and characterization, advanced manufacturing, and computational models. nCORE technical scope grew out of broad industry consensus regarding long-term (10-15 years) research needs. The nCORE program is coordinated with another research program, Joint University Microelectronics Program (JUMP) (https://www.src.org/compete/jump/).

A1. Research Areas of Interest

nCORE Mission: Explore fundamental materials, devices, and interconnect solutions to enable future high-performance computing/storage paradigms beyond conventional CMOS technology, beyond von Neumann architecture, or beyond classical information processing/storage.

- nCORE research is driven by fundamental research on emerging materials and devices with the potential to achieve significantly improved efficiency (at least 100x lower power), enhanced performance (at least 100x higher throughput), and new functionalities, beyond the capability of conventional CMOS technologies.

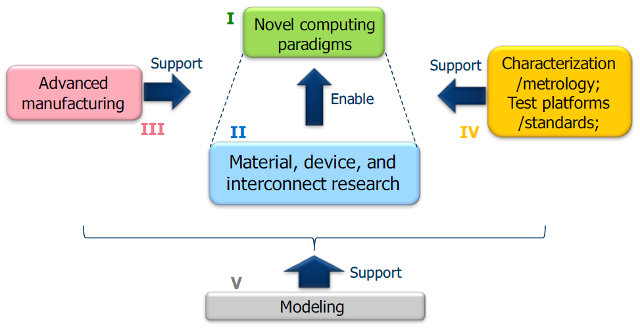

- Five research vectors together define an integrated comprehensive research scope of the nCORE program, as illustrated in Figure 1:

- Research Vector 1: Novel computing and storage paradigms, and theory of operation, beyond conventional CMOS devices, beyond von Neumann architectures, and beyond classical information processing and sensing

- Research Vector 2: Fundamental material, device, and interconnect research to enable novel computing and storage paradigms

- Research Vector 3: Advanced manufacturing and nanofabrication to enable the fabrication of emerging devices and systems

- Research Vector 4: Innovative metrology and characterization to support basic device and material research, and test platforms and standards to benchmark performance from devices up to systems

- Research Vector 5: Computational models to support basic research from emerging devices and materials to novel systems

Figure 1. The five research vectors of nCORE representing a vertically integrated research center

The five research vectors describe a vertically integrated research structure of a multi-university nCORE center, as shown in Figure 1. Vector 1 defines the high-level objectives of the research center. It includes a broad range of topics in novel computing and storage paradigms. A proposal should focus on selected topics relevant to the expertise of the center or team. Vector 2 is the core of the program that provide key enabling technologies to achieve the objectives defined in vector 1. A successful center proposal should be driven by innovations in Vector 2. Vectors 3, 4, and 5 all provide essential support in proposed research. A proposal should incorporate this vertically integrated research structure and address selected research components in each vector; however, it is not required to emphasize each vector equally. The center focus should be based on the expertise and the objective of the team. A proposal may emphasize a particular research vector that is essential to enable a comprehensive research structure represented by Figure 1.

The transformative and translational research anticipated to be the product of any nCORE center needs to be carefully documented, to include the thought process that guided the design of experiments to achieve the anticipated outcomes, as well as clear documentation of the methodology used in making measurements and analyzing data. Benchmarking activities, which are necessary for making informed decisions along the research path, should strive to assign confidence levels to reported parameters and facilitate model and theory development and validation. Ultimately, the results from different center activities should provide a foundation for defining the potential and limitations of materials, device designs, architectures, and computing paradigms.

The research in the nCORE program aims at enabling computing and storage paradigms to improve efficiency (e.g., low power or energy), to enhance performance (e.g., high throughput), and to create novel functionalities (e.g., cognitive capability, information inference). To achieve these goals, the research scope extends beyond CMOS device and design (e.g., low-voltage switch), beyond von Neumann architectures (e.g., compute in memory), beyond classical information processing/sensing, and beyond established algorithms in bio-inspired computing. Different from the JUMP focus on applications and systems, the nCORE program will focus on basic material and device research to provide enabling technologies for novel computing and storage paradigms beyond the capabilities of conventional CMOS. (Vector 1)

A paradigm shift in information processing and storage will require materials, devices, and interconnects with unique characteristics to provide superior performance, which may also necessitate unconventional and hitherto unknown mechanisms. Research in novel material systems and interface properties, such as III-V, low dimensional (0D-2D materials), multiferroics, ferroelectrics, magnetics, phase change, metal insulator transitions, will be essential. To support new material systems, new atomically-precise deposition and removal (etch and clean) methodologies are required with suitability for large area, low defect, tight geometries (sub-10 nm) and 3D integration, with selectivity and high-throughput. Paramount to a successful project will be a thorough understanding of heterogeneous system science, including bulk, surface, and interface, and their impact on device physics, without losing sight of the suitable scaling behaviors at sub 10 nm dimensions. As devices continue to shrink in size, the physics of reduced dimensional systems, including 2D, 1D, and 0D become increasingly important and quantum effects become both beneficial and deleterious. Ultimately, these devices need to be fast, capable of being thermally managed, robustly manufactured, and sufficiently low energy. Understanding the key characteristics required to make them both robust and reliable is crucial to the final design of future devices and essential to the development of next generation characterization tools and metrologies essential to manufacturing. Developing the knowledge infrastructure to characterize and weigh the tradeoffs as one transitions between reduced dimensions is integral to creating functional circuits and architectures. Understanding how to preserve, transduce, and transmit the essential properties of state variable over multiple length scales and across dimensions may also prove critical to future computing. To assess a study’s potential and progress, a plan for development, measurement and tracking of performance parameters and figure-of-merits (FOMs) is mandatory. (Vector 2)

Novel materials and devices require advanced fabrication technologies, e.g., atomic-scale precision placement, deposition, patterning, and etching. Advanced integration technologies (e.g., monolithic 3D) may enable functional diversification. With the number of processing steps approaching a thousand and the number of critical lithographic layers over fifty, the cost of manufacturing threatens the economic viability of semiconductor industry. As feature sizes approach molecular dimensions, the light source resolution is not the only roadblock anymore. Patterning pitfalls can be mitigated by new patterning material paradigms, precise material placement, planarization and etching techniques (e.g., atomic-scale selective deposition and etching). Other avenues for improvement include all mainstream materials, intelligent functionalizing (Jahn-Teller) or templating materials, and bio inspired manufacturing. Control of processing, interfaces, and defects is also crucial and will require advanced metrology tools capable of nanometer resolution. Stringent form factors for novel cyber-physical systems will require novel packaging techniques. Manufacturing research in new materials, processes, and tools with control at the molecular and atomic levels is critical to provide a cost effective path to the production of reliable future devices and interconnect architectures. Use of novel materials and processes may require novel testing techniques. (Vector 3)

The development of devices for beyond-CMOS and non-von-Neumann architectures will involve unconventional materials with new functionalities. A broad range of metrology and characterization techniques will be required, operating with high spatial resolution, high throughput, in situ and in operandi. The anticipated needs include both basic material metrology as well as comprehensive device characterization. Nanoscale materials characterization includes structural (e.g., crystallinity, composition, strain), electrical (e.g., polarization, charge density), thermal (e.g., conductivity, temperature), and magnetic properties (e.g., domain wall, coercivity, permeability). Equally important are high-throughput, fast-turnaround characterization methods of bulk and thin film properties with key ties to device performance. Rapid device characterization, including performance, energy efficiency, and reliability, is a critical component needed to close the loop between materials properties, device simulation, and performance at both device and system levels. Real-time measurements of electromagnetic fields, charge, magnetization, temperature, crystallinity, and strain in nanoscale devices need to be correlated with measurements of performance and reliability. Finally, metrics, protocols, and test platforms must be developed in order to rationally optimize devices and architectures for new computing paradigms. (Vector 4)

Computational capabilities need to be developed spanning from ab initio calculations and physics-based effective models that provide predictive treatment of material discovery and manufacturing process simulation capabilities, to electronics design automation (EDA) tools that can deliver complete systems including logical/physical design, simulation, and verification for the novel computing paradigm it supports. Modeling is key in benchmarking, characterization, fabrication, data analysis, parameter extrapolation, and process simulation and control. To obtain accurate material and device models, clear understanding of physical mechanism and verification from experimental feedback are essential. The compact models to aid device level design may be developed based on underlying physical mechanisms inferred from accurate material and device modeling. Future systems and circuits that are designed and built specifically for implementing revolutionary non von Neumann computing paradigms will require major innovation in the design flows and tools that will enable the creation of such systems. It is conceivable that the new systems may require radically different approaches for each of the major design steps (e.g. statistical verification methodologies). (Vector 5)

Note that nCORE does not intend to fund efforts overlapping with JUMP research. If applicable, proposers should explicitly state how the work in the nCORE center is significantly differentiated from any similar work proposed in JUMP, particularly if there is any overlap in PIs.

Proposers are encouraged to reference the nCORE website (https://www.src.org/program/ncore/) and “nCORE Research Scope” document for additional information and suggested research topics.

A2. Proposal Process

This solicitation is open to all U.S. universities and shall be conducted on a competitive basis. Universities should join together to achieve the depth and scope needed to address the technical content of this solicitation, as nCORE research will be funded through interdisciplinary, multi-university Centers. Proposed collaboration among PIs and universities in the form of Centers should identify a lead university and lead PI for purposes of an award. All awards are conditioned upon consummation of a sponsored research agreement with the Consortium. Cross-sharing between universities is strongly encouraged, but only U.S. universities will be considered for funding.

It is strongly encouraged that the number of PIs and universities involved be limited to a reasonable number for the total budget, to ensure that each PI is getting a critical mass of funding. No formal minimum amount per PI per year is being stipulated, but in general each PI should have sufficient funds to fully support at least 1-2 students or post-docs within this program.

Investigators should ensure that their proposals address the following essential attributes:

- A research plan which contains a compelling and well-articulated vision on how the center’s work will result in key learning about specific materials, devices, and/or architectures that support the nCORE's research agenda described in Sec. A1.

- Clear explanation of how the proposed research will be unique or how it will be distinguished from related university research in nanoelectronics. (nCORE aims to support research which complements but does not overlap that of other industry-sponsored university research programs.)

- A list of clear milestones that will result in sufficient learning about the proposed technology to prove its future potential as a platform that can scale beyond the expected limits of CMOS technology for computation/storage.

- A reasonable scope of research which can be realistically executed with available resources and in accordance with sound cost management.

- A description of the host institute’s policy and history of successful industrial collaboration regarding the exchange of staff, recruiting of students, intellectual property agreements and previous successful collaborations with industrial partners.

- A statement addressing the plans for matching funds from university, state or federal sources to leverage the funds from nCORE. There is no formal requirement for cost sharing, but proposals that include matching funds and infrastructure investments will be considered favorably in the review process.

- A statement addressing the availability of facilities and resources needed to help make the proposed project successful. This should include any plans for collaboration with NIST or other labs / institutes / nCORE member companies for doing joint work, if applicable.

- A Data Management Plan (DMP) in compliance with the requirements of NIST Policy 5700.00, Managing Public Access to Results of Federally Funded Research https://www.nist.gov/sites/default/files/documents/2017/05/09/Final-P-5700.pdf and NIST Order 5701.00, Managing Public Access to Results of Federally Funded Research https://www.nist.gov/sites/default/files/documents/2017/05/09/Final-O-5701_0.pdf, or any successor Policy and Order.

NIST engagement plan: NIST is collaborating with the NST Consortium pursuant to a cooperative agreement that is subject to the Department of Commerce Financial Assistance Standard Terms and Conditions which terms shall flow down and be applicable to any awards under this solicitation. Consistent with the Final Office of Management and Budget Guidance Implementing the Federal Grant and Cooperative Agreement Act, 43 Fed. Reg. 36860-65 (Aug. 18, 1978), NIST shall have certain special powers with respect to an award under this solicitation, including among other things: (i) authority to halt immediately an activity if detailed performance specifications are not met; (ii) requiring that an a award recipient meet or adhere to specific procedural requirements before subsequent stages of a NIST-funded project may continue; and (iii) limiting an award recipient‘s discretion with respect to scope of work, organizational structure, staffing, mode of operations and other management processes, coupled with close monitoring or operational involvement during performance.

The proposal must include a detailed plan for collaboration with NIST researchers to conduct research at NIST sites to utilize the testing, characterization, fabrication, and modeling resources at NIST. The proposals must identify research projects suitable for NIST’s mission, suggest NIST divisions, laboratories, and researchers for collaboration, and develop detailed execution plans and timelines for the university researchers (including PIs, post-docs, graduate and undergraduate students) to work at NIST. The quality of this NIST collaboration plan will be an important factor in the proposal selection process; however, the execution of the NIST collaboration plan will be separated from the start of Center research, pending availability of NIST resources and personnel. After the selection and launch of the nCORE centers (e.g., after year 1), requests for proposals may be released for supplemental funding to conduct collaborative research at NIST. With on-going nCORE research, the supplemental funding approach can target high-priority projects for NIST and fill research gaps. Proposers are encouraged to reference the NIST website (www.nist.gov) and nCORE website (https://www.src.org/program/ncore/) for more information about resources for NIST collaboration.

The proposals will be reviewed by the nCORE Science Advisory Board (SAB), which comprises senior researchers from the participating companies and NIST. In addition to financial support appropriate to pursuing mutual interests of the investigators and nCORE, there will be an opportunity to collaborate with industrial researchers from nCORE participating companies and from NIST. The research results should be widely disseminated, and publication in technical journals and presentations at conferences is strongly encouraged. Participation by funded researchers in the nCORE reviews, and potentially at industry/government sponsored workshops and meetings, is required. There is an annual review of the overall nCORE program, as well as annual on-site reviews of each center and semi-annual reports submitted to SRCco from each center. All publications, reports and review materials are to be posted on the nCORE website.

Evaluation, technical review and recommendations on the proposals will be done by the nCORE SAB, and the final decision on the awards will be made by the nCORE Governing Council.

A3. Program Scope and Planned Funding Level

The proposals should target funding size of $1,500,000 per year, with funding allocated on a yearly basis. Project proposals should be based on a three-year research plan with a potential two-year extension pending performance and funding availability. All funding after the first year will be contingent upon successful performance, as evaluated by the nCORE-NIST collaboration, and availability of funds. Following proposal selection, research agreements will be negotiated with awardees as appropriate, with the research expected to start on January 1, 2018. Any potential for additional funds from university, state or federal sources to match the nCORE funds should be included in the proposal and will be considered in the review process. These are expected to be included in the final formal budget, and will be tracked just as the nCORE funds are. Not all areas of interest may necessarily be funded, and the titles of the broad areas of interest are not synonymous with the names of the current or planned research agendas, nor are there any implications that an area of interest cannot accommodate more than one research effort.

B. Proposal Guidelines and Schedules

B1. Purpose, Format, Content and Length of Solicited Proposals

Solicitation Purpose and Process

In order to permit selection of the proposals most likely to advance the nCORE research goals, proposals are being solicited from investigators to address the nCORE agenda in Sec. A1. The proposals are due electronically by 5:00 p.m. Eastern Standard Time on September 29, 2017. The process and address for submitting these proposals is described below.

Proposal Format, Content and Length

Go to: https://www.src.org/app/proposal/submit/ to download the nCORE Template Package and read the Guide to Online Proposal Submission. In order to submit a proposal you will need to obtain a proposal number by e-mailing proposal.admin@src.org.

Use the subject line "nCore Proposal ID", and include this information in the email:

- Title of proposal

- University name (U.S. universities only)

- Principal Investigator's (PI's) university phone and email address

- Which nCore Research Vector(s) are the key driver(s) of the proposal (refer to the Center Research Overview table in the template download to identify)

The proposal format is:

- When you first enter the Submit a Proposal Submission page you will be prompted to complete the cover page. After completion, you will need to print the cover page you have just created and gather the necessary signatures.

- A Center Research Overview (included in template download), consisting of:

- Table of Contents keyed to the page numbers of the proposal sections.

- An Executive Summary, a one- to two-page description of the proposal and key features.

- Description of the center research objectives, themes, project portfolio, and structure. This section should show the total planned center portfolio, structured around specific research the center will pursue.

- Statement of Work, to include a one-page table of projects/PIs organized by research themes, followed by description of each project including a description of the research, goals, fit to nCORE objectives and to a specific research theme, and a timeline of key milestones.

- The availability of the resources necessary, including plans for receiving matching funds from university, state, or federal sources to leverage nCORE funding.

- The Center’s plans for collaboration with NIST and industry. The NIST engagement plan should include detailed proposal of projects and personnel as well as funding.

- Management plan including center leadership, program evolution, facilities, etc.

- A proposal for (i) the licensing of intellectual property (IP) to SRCco with the right to sublicense nCORE participants, and (ii) the disclosure of and access to blocking background IP (“BIP”).

- List of key personnel and relevant publication record and references.

- Catalog Page (included in template download), lists tasks under theme.

- A Data Management Plan (DMP).

- A full detailed Budget (included in template download) broken down by theme and university for the funding period requested, including the matching funds from university, state, or federal sources.

B2. Proposal Submission Process and Related Information

Submission Process

Electronic submission of all proposals is required. Please contact SRC proposal administrator (proposal.admin@src.org) for a Proposal Number before attempting to upload your proposal. (See B1 above). Please address all questions to An Chen, nCORE Director (an.chen@src.org) and Mary Altman (mary.altman@src.org).

Disclosure of Proprietary Information

All proprietary portions of proposals must be clearly marked. Restrictive notices notwithstanding, proposals may be handled and read for purposes of evaluation by SRCco, nCORE Participants, NIST officials and selected external reviewers.

Intellectual Property

It is critically important to SRCco that in return for sponsoring research, it obtains worldwide, non-exclusive, irrevocable, fully paid-up, royalty-free license rights to all foreground technology, inventions, or other intellectual property (including trade secrets and rights in proprietary information and/or know-how) developed under the award at no additional cost, with the right to sublicense nCORE participants. Awardees may own and are free to license such IP to other entities. Certain IP rights are to be provided to NIST as required by statute. SRCco may be available as a resource, to assist awardees strategically and financially, as appropriate, to develop IP rights arising under an nCORE award.

Blocking Background Intellectual Property

SRCco funds University research with the objective that SRCco and participants will have the freedom to practice the results of the research. The existence of BIP of any party can seriously impair or even block the ability of SRCco and participants to exercise this freedom to practice. Therefore, SRCco seeks access to any and all background intellectual property needed to exercise its rights to and implementation of the foreground intellectual property. Awardees agree to identify and provide access to SRCco to relevant background intellectual property. SRCco is seeking rights in accordance with the SRCco guidelines Regarding Background Intellectual Property (file removed).

B3. Evaluation Criteria and Selection and Award Process

Evaluation Criteria

The selection criteria used in the technical review of the proposals, in order of relative importance and priority, are:

- Overall scientific and technical merit, including: (a) Impact of the proposed work on the nCORE research agenda; (b) Plan for producing data necessary to prove-out a new technology; (c) Ultimate potential of the technologies being pursued.

- Ingenuity, novelty, and feasibility of the proposal.

- Investigator(s) capabilities and related relevant experience.

- Access to the needed personnel, resources, facilities, equipment, and data to perform the work.

- The potential for leveraging nCORE funds with university, state, and federal funds.

- Quality of the collaboration plan with NIST and industry.

- Intellectual property issues, policies and procedures that may preclude timely execution of the contract.

Selection and Award Process

Proposals will be evaluated by a Proposal Evaluation and Selection Committee, comprised of a group of senior researchers from nCORE participating companies and NIST. The proposer will be notified of selection or non-selection in a timely manner.

All non-selected proposals will be destroyed, except one copy which may be retained for file purposes, unless the applicant has requested that the proposal be made available for consideration of alternate funding by other nCORE participating company funding instruments.

Not all proposals submitted in response to the invitation by SRCco and selected in the proposal review will be funded. Decisions to fund proposals will be based on funds available, scientific and technical merit, and potential contribution and relevance to the nCORE goals. All proposals selected for award will be funded through SRCco and will be subject to oversight by SRCco.

Any awards are tentative pending formal agreement of the fellow’s host institute to accept and administer the funds in accordance with a research agreement with SRCco. The investigator(s) will be expected to facilitate administrative matters if needed.

B4. Solicitation Schedule

Proposal Timetable:

| Event | Deadline |

| Publication of Request for Proposal | July 28, 2017 |

| Deadline to submit Proposals to SRCco | September 29, 2017 |

| Awards Announced | November 30, 2017 |

| Award Start Date | January 1, 2018 |