LEAST Researchers Develop TFET SPICE Model

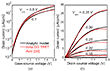

A compact tunnel field-effect transistor (TFET) SPICE model was completed and released to the LEAST circuit design community by researchers at the University of Notre Dame. The model, based on the Kane-Sze formula, captures the unique features of the TFET, including the decrease in subthreshold swing with drain current and the superlinear onset of the output characteristic. The model has fairly general validity and is not specific to a particular TFET geometry. Good agreement is shown with published atomistic simulations of an InAs double-gate TFET with gate perpendicular to the tunnel junction and with numerical simulations of a broken-gap AlGaSb/InAs TFET with gate in parallel with the tunnel junction. The model was implemented in HSPICE and AIMSPICE for both n and pTFETs.