# 2011-2015 SRC-GRC Strategic Plan

Limited Distribution Notice

Distribution of the material in this document is limited to employees of SRC-GRC member companies or participating government agencies.

# 2011 – 2015 SRC-GRC Strategic Plan Table of Contents

| Section I                                       |    |

|-------------------------------------------------|----|

| Executive Summary                               | 4  |

| Section II                                      |    |

|                                                 |    |

| SRC-GRC Strategic Planning                      |    |

| Overview                                        |    |

| SRC-GRC Partnerships                            | 9  |

| Section III                                     |    |

| SRC-GRC Research Program                        |    |

| Computer-Aided Design and Test Sciences (CADTS) |    |

| Integrated Circuits and Systems Sciences (ICSS) | 17 |

| Nanomanufacturing Sciences (NMS)                |    |

| Device Sciences (DS)                            |    |

| Interconnect and Packaging Sciences (IPS)       |    |

| Cross-Disciplinary Semiconductor Research (CSR) | 40 |

## Section IV

| SRC  | Supp | orting | Operations |  |

|------|------|--------|------------|--|

| SILC | Supp | or ung | Operations |  |

| Value Infrastructure Management     | 42 |

|-------------------------------------|----|

| Student Relations                   | 45 |

| Contracts and Intellectual Property | 48 |

I. Executive Summary

# I. EXECUTIVE SUMMARY

## **OVERVIEW**

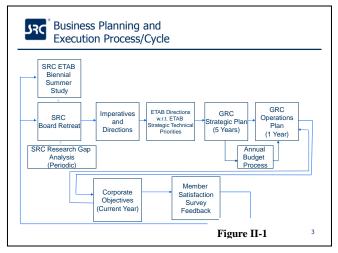

During the spring of each year, SRC business planning includes development of an SRC-GRC Strategic Plan, covering the ensuing five years (2011-2015). The planning process continues in the fall of each year with the development of an Operations Plan for the next calendar year. The GRC Strategic Plan is developed by various Technical Advisory Committees/Boards in conjunction with SRC Directors and managers of corresponding functional areas. The plan is reviewed by the appropriate representatives of member companies, the OCE and finally, the SRC Board. The plan becomes a plan of record after the SRC Board approves it in 2Q/3Q of the year.

## STRATEGIC PLANNING PROCESS

The development of these plans utilizes outputs from various forums and analyses. SRC has periodically continued to conduct a Research Gap analysis to assess the amount of research investment necessary to address the ITRS challenges as compared with the actual investment occurring worldwide. This analysis highlights the criticality of research needs and respective shortfalls in funding, thereby providing a backdrop for the Strategic Plan. Additionally, the SRC community conducts a biennial GRC ETAB Summer Study and an SRC Annual Board Retreat to derive long-term strategic technical and business directions. Based on the outputs of these two forums, the ETAB develops an annual list of top-down, strategic technical priorities. The SACCs and T-TABs develop the Strategic Plans of the various science areas using the inputs from the forum and analyses described above. All of the information from these sources is then incorporated into the strategic technical priorities that are decided at the end of the annual ETAB strategic planning meeting. These priorities are the starting point for the plans shown in **Section III**. The ETAB strategic planning strategic priorities resulting from the 2010 ETAB Strategic Planning meeting are reproduced here:

- Scaling to Ultimate CMOS: Processes, Materials, Devices, Packages, and Systems

- Analog/Mixed Signal: Processes, Materials, Devices, Packages, and Systems

- Memories: Materials, Devices, Circuits, and Subsystems

- Low Power Architecting: Devices, Circuits, and Systems

- Power, Thermal, and Energy Management

- Design Productivity for Circuits and Systems

- Application-specific Integration of Diverse Technologies

- 3D IC Architecting: Technology, Design, Test, and CAD

- Multicore Homogeneous/Heterogeneous Systems

- Reliable, Resilient and Robust Technology, Circuits, and Systems

- ESH Stewardship for Materials, Processes and Energy

The specific strategic directions for each science area and thrust are outlined here. Each of these thrust level areas of emphasis are determined by the SACCs and T-TABs after the ETAB strategic priorities are set.

## **COMPUTER-AIDED DESIGN AND TEST SCIENCES (CADTS)**

The design-related priorities in 2011 will have an overarching emphasis on power and energy, design for manufacturability, productivity, reliability and resilient robust systems. For digital technologies, the

emphasis is on variability, low power, multiple domains (voltage, clock, frequency, etc.) while analog topics include low voltage, synthesis, automated layout, test, and verification. System-level design issues include verification and test, software, multicore, 3D, reliability, memory subsystems, and multicore homogeneous/heterogeneous systems. Test issues include statistical test methods, more on chip self-test, mixed-signal, and 3D. Verification at all levels continues in importance.

#### INTEGRATED CIRCUIT AND SYSTEMS SCIENCES (ICSS)

The organization of thrusts into Circuit Design and Integrated System Design is working well and the crosscut themes of Compact Modeling, Mixed-signal, and Memory help segment the research. As the line between design and manufacturing becomes blurred, there exists increasing need and emphasis on cross science area collaboration. Priority changes from last year include an increased focus on interdisciplinary work (DS, IPS, CADTS). Areas of particular design importance include cost/yield, robustness, emphasis on low power systems, power management, and THz design. System-level focus on hardware/software approaches to satisfy reliability, variability, power, and thermal constraints and a memory emphasis from cache cell/architecture to system level coherency issues.

## **DEVICE SCIENCES (DS)**

In logics, the overall priority for DS is to track and push ITRS-driven CMOS scaling towards limits. New materials and processes are sought after for this purpose. Some important areas are strain to improve mobility, high-k gate dielectrics and metal gate, source/drain junction and contact, alternate channel materials such as III-V and Ge, etc. In analog technologies, active and passive devices are increasingly important for mixed-signal applications as well as functional diversification. In memory, the priority is to develop novel non-volatile memories of non-charge-based types, such as ReRAM, FeRAM, and MRAM, to replace the floating-gate and charge-trapping types. Apart from technology development, DS maintains a balance in modeling effort which includes process and device modeling, and compact modeling of the aforementioned technologies.

## NANOMANUFACTURING SCIENCES (NMS)

NMS addresses strategic nanofabrication technology challenges in two primary thrust areas: Environment, Safety, and Health (ESH) and Patterning (PAT), with emerging secondary themes of Nanoengineered Materials, Metrology, and reducing variability. NMS's Center for Environmentally Benign Semiconductor manufacturing satisfies the dual challenge of sustainable and high performance fabrication technologies, with low ESH impact. PAT thrust focuses on low variability patterning materials, techniques, and models that enable new cost curves for nanoelectronics fabrication. Additionally, this thrust seeds strategic exploratory work in functional, application specific materials and a predictive materials-by-design capability. It also supports novel metrology concepts that address emerging nanoscopic characterization needs, such as nanoscale defects and embedded local interface structures.

## **INTERCONNECT AND PACKAGING SCIENCES (IPS)**

The current strategy is to increase the research focus on the interface area between BEP and PKG, which has been clearly defined and includes 3D research. The IPS is targeting the 16 nm node and beyond. BEP's top priority is to ensure the viability and reliability of Cu / low k interconnects. There are increased interactions with design to better define the needs and potential for different interconnect solutions. There is also an increased emphasis on predictive modeling, nanometrology capabilities and interconnect centric memory research. Packaging research continues to push thermal management and control, I/O, power delivery and fundamentals of lead-free solder and fracture. There is also a growing need to explore biologically compatible packages and board level electronic packages among other

applications to accommodate the functional diversifications needs of the industry. The interface area focuses on 3D, die/package mechanical interactions, passive integration, thermal management and functional diversification.

## **CROSS-DISCIPLINARY SEMICONDUCTOR RESEARCH (CSR)**

One of SRC's missions is to provide a strategic vision for the possible scenarios of both technologies and their applications in the longer term (e.g. 15 years from now). As a part of this effort, SRC-GRC launches exploratory research targeting long-term applications through CSR.

Specific areas to target this year are to support efforts to develop new initiative in bioelectronics and to conduct a forum in Abu Dhabi on minimum energy electronic systems. Other fundamental studies on bio-electronic micro-systems, memory technology analysis and others will be pursued.

## VALUE INFRASTRUCTURE MANAGEMENT (VIM)

The mission of SRC's Value Infrastructure Management (VIM) group is to provide the people, processes and infrastructure necessary to proactively support and promote all aspects of SRC's value proposition. In essence, the primary strategic role of the VIM group is to position SRC's core value-based business services to adapt and evolve in support of SRC's strategic direction in a timely, efficient and effective manner.

II. SRC Strategic Planning

## II. SRC- GRC STRATEGIC OVERVIEW

SRC business planning process, depicted in Figure 1, results in two documents that provide the basis of long-term directions and annual operations of SRC. Each year during the first two quarters, the SRC community develops a Strategic Plan covering the time horizon of the following five years. In the fall of each year SRC develops an Operations Plan for the next year. These plans are based on a number of from variety inputs resulting а of formal interactions SRC member among the representatives on advisory boards and the Board of Directors. In order to develop a foundation for the Strategic Plan, the OCE team conducts an annual assessment of long-term environmental trends in

our industry and resulting challenges. Based on this assessment, the team also develops a five-year strategic vision and responses to these challenges. This strategic vision is reviewed with the Board to receive their inputs and ratification.

This year, the SRC strategic planning and the SRC-GRC strategic planning will be separated into two separate plans. The SRC-GRC strategic plan is the subject of this document and deals with the SRC-GRC strategy. The SRC strategic planning will be done separately and will be developed directly with the SRC Board of Directors. The result of that plan will be the basis for the strategic imperatives.

#### **SRC-GRC STRATEGIES**

The SRC Science Area Structure has proven to be responsive to the research needs of member companies and aligns well with the Focus Center themes. We expect that this structure will be sustained during the 2011-2015 timeframe of this Strategic Plan. However, there is a continuing need for Cross-Science-Area thrusts (Cross-thrusts) of which there are nine.

The nine managed Cross-thrusts that are currently operative are (1) 3D (List) (2) Mixed-Signal Technologies (Yeh), (3) Metrology and Characterization (Herr), (4) Modeling and Simulation (List), (5) Reliability (List), (6) Memories (Ng), (7) Multicore (Joyner), (8) Interconnect (List), and (9) Design for Manufacturability (Joyner). SRC also participates in an annual reliability symposium with SEMATECH and other agencies. SRC will continue its membership in the Nano Computational Network sponsored by NSF at Purdue that is developing computational tools for the atomistic level modeling of semiconductor devices.

A concerted effort to coordinate the SRC-GRC research with the research of the Focus Center Research Program (FCRP) is managed through the Science Area Directors and program managers. Each Director has responsibilities for a Focus Center that is most closely aligned to his respective area (see **Table 1**). The role of SRC-GRC Research Management in the FCRP includes coordination of FCRP and GRC Research Programs, Organization of the industry feedback to FCRP faculty at the annual reviews, and generation of reports for DARPA and members, and identification of FCRP research highlights for the FCRP Web site.

| Focus Center | MSD     | IFC        | FENA     | GSRC        | C2S2         | MuSyC      |

|--------------|---------|------------|----------|-------------|--------------|------------|

| GRC- Manager | Kwok Ng | Scott List | Dan Herr | Bill Joyner | Dale Edwards | David Yeh  |

|              |         |            |          |             |              | Table II-1 |

In addition to the coordinating responsibilities that are detailed above, an extra step in the solicitation process is in place at the GRC proposal review stage for all researchers who have research interests in a Focus Center. This step requires the researchers to describe the differences and overlaps of the coordinated research to allow optimization of the funding decisions in order to benefit both programs.

There is also an active effort to keep the NRI projects and results coordinated with the GRC research portfolio. Particular attention is paid to the results coming from CSR projects that would be relevant to the NRI program.

## SRC-GRC PARTNERSHIPS

#### SIA

SRC expects to continue to support SIA initiatives to call to the attention of Congress and the Administration the vital importance of the semiconductor industry to the economic health of the United States, and, in particular, to the relative decline in federal support for basic research in Physical Science and Engineering.

## NSF

SRC expects to continue its productive partnership with NSF over the planning period. The ten year partnership with NSF to support the Engineering Research Center on Environmentally Benign Semiconductor Manufacturing concluded in 2006. SRC-GRC and SEMATECH are continuing to support a center at the University of Arizona in this area post 2008.

The NSF/SRC-GRC initiative originally entitled 'Silicon Nanoelectronics and Beyond (SNB)' operated under an addendum to an umbrella MOU and provides for SRC (and hence industry) involvement in the planning, selection, and review of NSF-sponsored programs arising from the annual NSF-wide Nano Science and Engineering (NSE) solicitation. We have renewed this MOU to integrate NSF projects that are of interest to our members into the SRC research dissemination processes for faculty who choose to participate. We are also in the second year of a 3 year joint program in multicore research. We are working closely with NSF and individual universities to target new choices for Engineering Research Centers to have research directions that are of interest to the semiconductor industry.

#### **STATE GOVERNMENTS**

SRC-GRC and the State of New York are jointly supporting the Center for Advanced Interconnect Science and Technology (CAIST) that is headquartered at the State University of New York at Albany and involves a substantial number of New York and university participants from other regions. We have joint programs with Texas (TxACE and CEMPI), with Georgia (IPC), and Arizona (ESH). These programs provide substantial leverage for member funds and serve as a model for other SRC/State research initiatives.

## NIST

SRC-GRC has also worked closely with NIST and we will seek ways to expand our domain of cooperation. The area of metrology and characterization will assume ever-increasing importance as the industry moves into the far-sub-nanometer regime. We have begun an interaction and cooperation in the area of device reliability and bioelectronics.

# III. SRC- GRC RESEARCH PROGRAM

## **OVERVIEW**

| Science Area: | Computer-Aided Design and Test Sciences |

|---------------|-----------------------------------------|

| Director:     | William H. Joyner, Jr.                  |

## MISSION

The Computer-Aided Design and Test science area has as its mission:

To promote diverse university research to strengthen member leadership in computer-aided design and test

- through tools and techniques that:

- reduce cost and time-to-market through productivity improvement and correctness assurance

- o take full advantage of technology advances through linkages to manufacturing

- enable high level/high value design

- through highly qualified graduate students who can fill key positions in member companies, and

- through strategic partnerships that leverage other funding sources

Member companies who employ SRC-supported students on summer internships, as postdocs, or as permanent employees are able to better extract the value of research in design tools and test techniques. Students can apply the results of their research, often immediately, in the industrial research and development environments of SRC members, giving them an advantage over those without the opportunity to guide and take early advantage of this work.

Design and test tools also can and must address cost pressures:

- by reducing time-to-market through the speedup of the logic and physical design process and the migration of this process to higher levels,

- by addressing product field failures through pre-manufacturing verification, efficient and effective manufacturing test, post-silicon validation, and cost-effective post-manufacturing infield testing, and

- by coupling with the manufacturing process to control cost and improve yield as feature sizes shrink.

#### **ENVIRONMENT AND TRENDS**

Highlights of the changing environment facing computer-aided design and test include:

- The CADTS ecosystem

- CAD vendors depend on industry as a whole; need multiple sources for research

- Design and CAD must do "due diligence" to extract highest performance from each technology node

- Designer productivity not keeping pace with design complexity

- Pre- and post-silicon validation an increasing focus due to time-to-market, lower average selling price, complexity factors

- CAD spans the design/manufacturing boundary; high level decisions must comprehend the effects on manufacturing and post-silicon

- The digital design environment

- 2-3 billion transistors on a chip (and increasing) with power constraints

- Voltage supplies approaching 0.7 V (possibly lower)

- Opposite pulls:

- higher-level design to improve productivity

- lower-level awareness to assure manufacturability

- DFV/DFT/DFR critical as variability, diverse operating modes and power management techniques increase

- Multi-cores, networks, true systems with 1012 ops/sec (challenge and opportunity)

- Emerging devices and new technologies

#### • The analog/mixed-signal/RFdesign environment

- Analog is still challenging from hertz to terahertz: fully integrated on chip, within package, or stand-alone.

- Tools challenges include:

- reliability assurance and temperature awareness

- analog/mixed-signal test

- automation for synthesis, physical design, verification

- variation-tolerant analog design and optimization tools

- tools for electromagnetic compatibility analysis

- Applications in safety, health and energy require highly robust and fail-safe designs

- Not scaling at the same rate as digital

- harder to get to work with advanced processes

- may need special processes and special devices

- may drive 3-D IC design tools

- Concerns remain about noise from digital circuits in SoCs with increased analog content

#### • The system design environment

- o Opportunity to exploit higher level design and verification for increased productivity

- o 3D issues pervade all science areas: test, synthesis, power are key

- o Software a major component of system design and affects CAD focus

- o System testing/verification an increasing challenge

- Power/thermal issues at multiple levels thermal variability a greater challenge

- Homogeneous and heterogeneous multi-core designs hold promise (power reduction), challenge (software and applications) also opportunity to gain CAD productivity

- Cyber-physical systems an increased focus

#### • CAD and test challenges

- Increased focus on reliability and resistance to failure with reduced ASP, higher volume, lower margins, test challenges

- Design productivity still key time-to-market critical

- "Correct-the-first-time" important to reduce re-spins

- Need to reduce size/cost of design teams

- Optimization and system-level design are key

- Post-silicon bring-up, validation, test

- o Mixed-signal/heterogeneous systems make test and verification more difficult

- 3D affects all thrusts

- Technology scaling and the resulting design rule explosion

- Observability obscured by complexity

Where do computer-aided design and test fit in the spectrum between fabrication technology and system design? Process technology and device/ process research provide devices and the ability to scale. Circuit/system design provides techniques to use these devices to accomplish a specific purpose. CAD and test provide the only productive interface between the two. Ever increasing design complexity decreases productivity and profitability and increases time to market. Tools and automation are the only viable mechanisms for dealing with this increased complexity of the design/manufacturing interface.

#### **PRIORITIES**

The SRC Executive Technical Advisory Board highlighted these design-related priorities in 2010:

- Analog/Mixed Signal: Processes, Materials, Devices, Packages, and Systems

Synthesis, physical design, test and verification

- Memories: Materials, Devices, Circuits, and Subsystems

- Memory subsystem test and validation

- Power, Thermal, and Energy Management

- System-level power and thermal estimation and reduction

- Design Productivity for Circuits and Systems

- High-level languages, real-time simulation and emulation

- o System-level exploration of specs, coverage, mapping, verification, test

- Application-specific Integration of Diverse Technologies

- Novel architectures for emerging application spaces

- 3D IC Architecting: Technology, Design, Test, and CAD

- 3D IC enabled applications

- 3D implications in multicore applications

- Multicore Homogeneous/Heterogeneous Systems

- 3D implications in multicore applications

- Memory subsystem test and validation

- Systematic post-silicon bring-up and debug

- Reliable, Resilient and Robust Technology, Circuits, and Systems

- DFM through robust and resilient design for both analog and digital

- Cross-system resiliency

- Stochastic design techniques and methodologies

- o Process aware synthesis and physical design tools

Design priorities emphasized in the 2009 International Technology Roadmap for Semiconductors include:

- Resilience / reliability

- Power management

- Design productivity

- System-level design, including analog/mixed-signal

- o Formal verification

- o Optimization/synthesis, including analog/mixed signal

- Design for manufacturability

- Variability issues

- Test issues

## STRATEGIC ACTION PLAN

- Classical challenges expected to remain difficult: power and energy, design for manufacturability, productivity, reliability

- Continue exploration of leading technologies for CAD

- Digital: variability, low power, multiple domains (voltage, clock, frequency, etc.)

- AMS: low voltage, synthesis, automated layout, verification, test

- System-level design: verification and test; software, multicore, 3D, reliability

- Thrusts and emphases:

- Design issues (low power/voltage, variability, resilience, high-level, productivity)

- Test issues (statistical test methods, more on chip self-test, mixed-signal)

- Verification issues (mixed-signal, coverage, post silicon validation)

- Link with other science areas as traditional boundaries blur

- Continue leveraging initiatives and cooperation with NSF, DARPA, States, CDADIC, FCRP, GRC SAs, others

|                                          | 2011            | 2012    | 2013 | 2014    | 2015 |  |

|------------------------------------------|-----------------|---------|------|---------|------|--|

| Logic-Physical Design                    |                 |         |      |         |      |  |

| DFM/variability <sup>(1,2)</sup>         |                 | sustain |      |         |      |  |

| Core/block level tools <sup>(2)</sup>    | sustain decline |         |      |         |      |  |

| Failure-resistance <sup>(1,2)</sup>      | grow sustain    |         |      |         |      |  |

| A/MS/RF <sup>(1,2)</sup>                 | gı              | ſOW     |      | sustain |      |  |

| Hi-level/syst/SOC tools <sup>(1,2)</sup> | g               | ſOW     |      | sustain |      |  |

| Diverse tech/arch <sup>(1)</sup>         |                 | s       |      |         | grow |  |

| Power/clock distribution                 | decline end     |         | end  | end     |      |  |

| 3D tools <sup>(1)</sup>                  | grow sustain    |         |      |         |      |  |

|                                        | 2011         | 2012    | 20      | 13      | 2014    | 2015 |

|----------------------------------------|--------------|---------|---------|---------|---------|------|

| Verification                           |              |         |         |         |         |      |

| Core technologies <sup>(2)</sup>       | sus          | tain    |         |         | decline |      |

| RTL/Coverage <sup>(2)</sup>            |              | sustain |         |         | dec     | ine  |

| System-level <sup>(1,2)</sup>          | gro          | w       | sustain |         |         |      |

| Software/microcode (1)                 | grow sustain |         |         | 1       |         |      |

| A/MS/RF <sup>(1)</sup>                 | grow         |         |         | sustain |         |      |

| Test                                   |              |         |         |         |         |      |

| Stuck-at fault                         | decline      | end     |         |         |         |      |

| System/SoC <sup>(1)</sup>              | gr           | OW      |         |         | sustain |      |

| Delay-based                            | dec          | e       | nd      |         |         |      |

| Correlation-based (2)                  | grow         |         |         |         | sustain |      |

| Post-silicon validation <sup>(1)</sup> | gr           |         | sustain |         |         |      |

| A/MS/RF <sup>(1)</sup>                 | gr           | ow      |         |         | sustain |      |

(1)=ETAB priority (2)=ITRS

#### **OVERVIEW**

Science Area:Integrated Circuits and Systems SciencesDirector:David C. Yeh

#### MISSION

To conduct research in advanced integrated circuits and systems design that will

- Exploit advances in IC technology while overcoming associated barriers and challenging conventional notions of the circuits and systems design space

- Develop a circuits and systems research portfolio that will provide exceptional value to our MCs with a focus on design-based performance gains

- Facilitate the training of highly-skilled graduates to help fill design engineering needs of MCs

In the circuit design space, the emphasis will be on advances for robust high-performance low-power digital logic and memory, analog, RF, and mixed-signal designs. In the integrated system design space, the emphasis will be on advances that enable robust and power efficient designs for both high performance and embedded systems comprised of silicon and software for diverse applications. Additional emphasis will be placed on defining algorithms and methodologies required for critical design activities in diverse application domains.

#### **ENVIRONMENT AND TRENDS**

As the semiconductor fabrication industry approaches the fundamental limits of CMOS device scaling, the device property improvements at each new technology node become harder to achieve. Thus, extracting the expected performance and economic advantages of moving to new process nodes is harder now than in the past. New design techniques are necessary to facilitate and augment the march towards using advanced processing nodes. The push to integrate more functionality on-chip and achieve higher performance to drive down the cost per transistor continues but this also encounters more obstacles with each succeeding process node. Modeling the parasitic effects and process variability that are critical for robust behavior (of both analog and digital components) is getting much more difficult. These factors increase the risk and thus, the uncertainty of recovering costs of doing designs in these advance process nodes. This is driving more companies towards design-based performance gains – extracting more out of existing technologies through the use of more innovative design. This is especially true for analog/mixed-signal applications. Furthermore, members' exploration of new application domains may drive research along possibly different vectors and this will have a critical impact on the portfolio in the future.

Some of the critical topics on the scaling path that impact design techniques include SRAM stability, self-testing and self-repairing systems, and dynamically reconfigurable circuits. This type of research will be targeted towards leading edge process nodes and the types of devices and interconnect that technology will enable. On the functional diversification and design-based performance gains front, work will need to address topics such as higher performance analog/mixed-signal design and efficient multi-core operation. Some of the subtopics include circuit architectures, embedded memory, software, I/O, and communications. As chip transistor counts reach several billion, the additional circuit and system complexity leads to long and difficult new product de-bug and launch cycles. Circuitry for built-in self-testing, self-calibration, and self-repair is needed to help overcome these issues. For many system applications, software as well as hardware has a strong impact on overall system performance. Thus, software is one of the keys to allowing dynamic response and optimization of power,

performance, reliability, and other system metrics. In the multi-core design space, this is especially true. Research on improving compilers and multi-core programming models, supporting programming, debug, and optimization needs of system developers is needed.

Long-term, the emergence of non-classical devices along with new diverse applications will dramatically impact design techniques. While some of these devices have appeared, such as double-gate structures, it is not too early to re-examine the design process to determine how to best take advantage of the new structures. New applications in areas such as medical, energy, and specialized automotive electronics are emerging. Even so, the same design issues of power, reliability, test, manufacturability, and accurate modeling will remain substantial challenges.

- Technology driven constraints impact circuits and memories

- Process variability, leakage, low-Vdd, new devices (eg. FinFETs)

- Increased transistor count worsens technology constraints

- POWER will always be an issue even beyond CMOS

- Increased statistical variation → analysis requires more "sigmas"

- Increased probability of reliability-induced failure: SEU and aging

- Resilient circuits and architectures will be essential

- Design complexity increases faster than transistor count

- SoC/SiP integration of multiple functional blocks + software

- Long and difficult new product development and launch cycles, including software development and debug

- Challenge to optimize digital and analog circuits

- Diverse applications drive architecture/ IP/circuits/ software

- Design constraints cover power, performance, cost, safety, ...

- Emphasis on multi-core and system reliability

- Software concurrency, tools, debug, verification, programming model

- The spectrum of research is broad and interdisciplinary

- Digital, analog, mixed-signal, RF, memory & I/O

- o Novel structures: e.g. multi-gate, 3D integration, & carbon-based

- Reliability impact: cause-effect and solutions

- Design research on the CMOS scaling path continues

- Adaptive systems: self-test & self-repair

- Dynamic reconfigurable circuits & systems

- $\circ$   $\,$  Covers frequencies of interest from Hz to hundreds of GHz  $\,$

- Focus on design-based performance gains

- Supplementing technology-based gains

- High fab cost for PI's constrains research focus

- $\circ$   $\;$  Need is to focus on areas where universities add value

## **PRIORITIES**

In 2009, the International Technology Roadmap for Semiconductors underwent a major update and the Design Chapter still states that the cost of design is the greatest threat to continuation of the semiconductor roadmap. Both hardware and software are included in this cost and are expressed as silicon complexity and system complexity. The revision also highlights five cross-cutting challenges: design productivity, power management, design for manufacturability, interference, and reliability.

• Silicon Complexity

- o Non-ideal scaling of device parasitics and supply/threshold voltages

- Coupled high-frequency devices and interconnects

- Manufacturing variability

- o Complexity of manufacturing handoff

- Scaling of global interconnect performance relative to device performance

- Decreased reliability

- System Complexity

- o Reuse

- $\circ \quad \text{Verification and Test}$

- o Cost-driven Design Optimization

- Embedded Software design

- o Reliable Implementation Platforms

- Design Process Management

The SRC GRC ETAB also gives guidance on priorities and those have strong overlap with ICSS. The following list of priorities has been extracted from the 2014 ETAB Priorities as those with the highest weighting.

- Analog and Mixed-Signal Design

- Synthesis, physical design, test and verification

- o Ultra-low powered digital and analog circuits

- Compact Models: device (active/passive)

- High performance low power signal I/O

- RF and mixed-signal circuits for M2M communication

- Homogeneous/Heterogeneous Multi-Core Architectures

- o 3D implications in multicore applications

- Highly parallel system architectures

- New explicit programming models for embedded and general purpose multicores

- o Software

- Methods for systematic post silicon bring-up and debug

- o Memory subsystem test and validation, including coherence assurance

- System level exploration specification, coverage, mapping

- Memories

- Non-volatile memory: eg. phase-change

- Novel cell and system architectures

- Coping with Variability/Reliability Issues

- Manufacturing options for reducing variability and enhancing reliability

- Design for manufacturability through robust design for both digital and analog (regularity, statistical optimization, configurable redundancy, etc)

- Resiliency across the system including process variability, tunable with respect to reliability, and adaptable circuits and architectures

- Methods to assess system reliability in the face of new failure

- Stochastic design techniques and methodologies

- Merging of configurable design, fault diagnosis, and testing

- Autonomic approaches for variability and aging compensation

- o Deterministic fabrication methods

- Design Solutions for Thermal/Power

- o System-level power and thermal estimation and reduction

- o Active feedback between thermal solutions and processor

- Functional Diversification Applications

- 3D IC enabled applications

- o Integration of key components eg. sensors, energy harvesters and storage

- Systems level: hi-level languages, real-time simulation and emulation

- Cross-functional integration of semiconductor systems design with human factors and cognitive systems research

- Novel architectures for emerging application spaces

#### STRATEGIC ACTION PLAN

Looking forward, the strategies and actions are still driven by the member companies through various channels, which include inputs at the SACC, ETAB, and BoD levels. The organization of thrusts into Circuit Design and Integrated System Design is working well and the crosscut themes of Compact Modeling, Mixed-signal, and Memory help segment the research. With the new ETAB allocation at the thrust level, the influence of the SACC on the portfolio evolution has been decreased. Even so, there still is a balance between the Circuit Design and Integrated System Design thrusts, with support for a small amount of Compact Modeling. The SACC was also in favor of a small amount of Director's Discretion funding. The portfolio is also influenced by the work proposed in response to our solicitations, which may include ideas not anticipated in the process and our desire to only fund excellent research.

As the line between design and manufacturing becomes blurred, there exists increasing need and emphasis on cross science area collaboration. Leveraged funding dollars are still highly valued and ICSS participates in several activities with NSF, CDADIC and MISCIC. Other new sources of leveraged funding will be considered if any appear beneficial for member companies. Finally, delivering value to the members in the form of relevant research and hirable students skilled in design remain our highest priorities.

- New Changes in Research Priority (since last year)

- Increased focus on interdisciplinary work (DS, IPS, CADTS)

- Design research for silicon CMOS, reflected in Needs documents

- Objective functions include power, performance, reliability, thermals, cost/yield and robustness

- o Underlying processes cover leading-edge to mature

- Areas cover digital, analog, mixed-signal, RF, and memory

- Abstraction from circuit level to systems architectures

- Product usage from general purpose to application-specific

- More diverse systems/applications research; embedded and high performance multicore architectures; 3D exploration; power gating optimization

- Circuits and systems research for applications in health, medical, and security: emphasis on low power systems, power management, and THz design

- System-level focus on hardware/software approaches to satisfy reliability, variability, power, and thermal constraints

- Memory emphasis from cache cell/architecture to system level coherency issues

- Monitor long-range research FCRP, NRI, etc., engage when ready

- Continue to increase value to member companies

- e-Workshops in ICSS, including monthly TxACE e-workshop,

- e-Kickoffs for new programs

- Help members identify/hire excellent students

- Invite final year students to reviews, present posters, and meet Members

- Remote access to reviews; travel assistance through RCP funds

- $\circ$  File IP where there is value

- o ICSS newsletter

- o Improve design-to-fab infrastructure for PIs

- MOSIS special pricing/GRC fab \$ match program

- Investigate other opportunities for fabrication

- Work across science areas where appropriate

- CADTS system tools; DS predictive CMs; IPS packaging;

- Partnering with other entities for leveraging

| Circuits                                        | 2011 | 2012    | 2013    | 2014 | 2015 |  |

|-------------------------------------------------|------|---------|---------|------|------|--|

| Memory                                          |      |         | sustain |      |      |  |

| Functional<br>Diversification -<br>Applications | grow | sustain |         |      |      |  |

| Analog & MS Design                              | grow | sustain |         |      |      |  |

| Homogeneous/<br>heterogeneous<br>multicore      |      | sustain |         |      |      |  |

| Coping with<br>variability and<br>reliability   | grow | sustain |         |      |      |  |

| Design solutions for thermal/power              |      | sustain |         |      |      |  |

| Systems                                         | 2011    | 2012    | 2013 | 2014 | 2015 |  |  |

|-------------------------------------------------|---------|---------|------|------|------|--|--|

| Memory                                          |         | sustain |      |      |      |  |  |

| Functional<br>Diversification -<br>Applications | grow    | sustain |      |      |      |  |  |

| Analog & MS Design                              | sustain |         |      |      |      |  |  |

| Homogeneous/<br>heterogeneous<br>multicore      |         | sustain |      |      |      |  |  |

| Coping with<br>variability and<br>reliability   | grow    | sustain |      |      |      |  |  |

| Design solutions for thermal/power              | grow    | sustain |      |      |      |  |  |

## **OVERVIEW**

| Science Area: | Nanomanufacturing Sciences (NMS) |

|---------------|----------------------------------|

| Director:     | Daniel Herr                      |

#### MISSION

The mission of NMS is to deliver value by developing and providing early access to evolutionary, breakthrough, and high impact material, process, and metrology technologies for scaled CMOS, targeting a half pitch of  $\leq 16$  nm, and analog/mixed signal technologies, including:

- Low variability, centered, and cost effective nanofabrication options that enable extensible scaling [≤16 nm];

- Functional diversification of charge-based technologies, which may be in addition to scaling options that increase performance and functionality; and

- High-performance and sustainable options that enable 3-D applications;

## **ENVIRONMENT AND TRENDS**

The semiconductor industry's growth rate relies on continuously enhanced functional density to provide increasing value. However, it is becoming increasingly difficult to manage variability, cost, reliability, yield, sustainability, and factory operations with conventional scaled subtractive/damascene processing alone. This trend implies an increasing number of potential insertion opportunities for breakthrough innovations in materials and nanofabrication technologies that address these emerging digital and analog/mixed signal challenges.

#### **PRIORITIES**

The following high level strategic research priorities are aligned with the NMS mission and driven by the 2010 ETAB identified critical research needs:

- Centered, low variability fabrication technologies: Demonstrate that the percent of manufacturing variability need not increase with functional density, i.e. with respect to dimension, overlay, placement, composition, architecture, etc. This includes the development of predictive models that provide insight into key nanomanufacturing tool-material-process trade-offs and their synergistic impact on reducing material, process, structural and property variability;

- New cost curves for nanoelectronics fabrication: Develop novel materials, modeling, process and equipment options that:

- Enable extensible nanoelectronics fabrication, defect detection, and yield management into the sub-10 nm domain;

- Strengthens the predictive capabilities of the computational lithography infrastructure;

- Leverage the existing fabrication infrastructure;

- **Functional diversification:** Design, identify, and enable the integration of customized materials with electronically useful functionality for high value application opportunities, which includes an emerging emphasis on predictive materials by design and quantitative material structure-property correlations;

• **Sustainable, high performance fabrication:** Extend sustainable, benign, high performance nanomanufacturing technologies into the sub-10 nm domain.

This set of challenges provides a framework for assessing the potential of proposed and continuing research to achieve critical science area objectives.

#### STRATEGIC ACTION PLAN

Note: [<sup>1</sup> ETAB rating of near term/long term critical research challenge; <sup>2</sup> ITRS challenge]

**Nanomanufacturing Sciences Research [NMS], Overall:** NMS' 2011-2015 research strategy is designed to:

- Identify and address strategic member/ETAB and ITRS identified needs;

- Leverage, engage, and influence targeted government and regional initiatives;

- Engage tool suppliers early in the research cycle;

- Enhance GRC/NMS-FCRP-NRI synergy, coordination, and networking;

- Evolve thrusts to anticipate and reflect non-traditional drivers.

**Patterning Research [PAT]:** This thrust creates and enables high-impact potential patterning options for low variability extensible scaling, centered at 16 nm and beyond, and scaling independent technologies, which address member-identified and projected ITRS difficult patterning challenges.

- 2011-2013: Assess potential of directed self-assembly for insertion in 2016.

- 2011-2015:

- Address the patterning variability challenge, such as through an increased emphasis on predictive computational lithography and process aware compact models;

- $\circ~$  Develop critical knowledge-base of post-NGL patterning options;

- $\circ~$  Identify and address strategic member-identified patterning needs.

|                                                                                                                                         | 2011    | 2012            | 2013 | 2014 | 2015 |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|------|------|------|

| Patterning Options that Enable Reduced<br>Variability, Extensible Scaling, and<br>Enhanced CD and Process Control <sup>1(28/28),2</sup> | start   | grow            |      |      |      |

| Directed Self-Assembly <sup>1(26/23),2</sup>                                                                                            |         | sustain grow    |      |      |      |

| Process Aware Compact Models, such as Directed Self-Assembly. 1(26/23),2                                                                | start   | grow            |      |      |      |

| NGL Extensibility / Limits <sup>1(26/23),2</sup>                                                                                        |         | sustain decline |      |      |      |

| Alternate/Non-Traditional<br>Patterning <sup>1(26/23),2</sup>                                                                           | sus     | sustain grow    |      |      |      |

| Nanoimprint Patterning <sup>2</sup>                                                                                                     | decline | end             |      |      |      |

**Nanoengineered Materials [NEM] (Currently Positioned Under the Patterning Thrust):** This thrust explores emerging research material and process options that address strategic member scaling and analog/mixed signal needs.

• 2011-2015: Launch targeted seed projects that explore prioritized needs and uncover emerging opportunities;

- 2011-2015: Increase the emphasis on developing predictive material and process TCAD tools that enable a functional and structural materials-by-design capability.

- 2011-2014: Establish a formal process for efficiently communicating breakthrough results with other thrusts and science areas.

|                                                                                                          | 2011             | 2012         | 2013 | 2014    | 2015 |

|----------------------------------------------------------------------------------------------------------|------------------|--------------|------|---------|------|

| Functional Diversification on CMOS,<br>including materials for enabling 3D<br>IC applications*1(28/29),2 |                  | grow         |      | sustain |      |

| ITRS-Identified Emerging Research<br>Materials [CMOS and A/MS] <sup>1(26/25),2</sup>                     | start grow       |              |      |         |      |

| Process & Material TCAD <sup>1(25/26),2</sup>                                                            | su               | sustain grow |      |         |      |

| New CMOS and Analog/Mixed<br>Signal Materials/Processes <sup>1(24/26),2</sup>                            |                  | start        | grow |         |      |

| Deterministic Fabrication*1(18/18),2                                                                     | sustain decline? |              |      |         |      |

**Metrology and Nano-Characterization Research [MET]:** This cross-thrust addresses strategic member company and ITRS-identified nano-characterization and metrology knowledge gaps. It explores emerging and enabling sub-10 nm measurement options.

- 2011-2012: Secure resources to address GRC/FCRP/NRI nano-characterization gaps.

- 2011-2015:

- Increase and maintain visibility of metrology results across thrusts and science areas.

- Update assessment of GRC/FCRP/NRI nano-characterization gaps.

- Leverage and engage strategic relevant metrology initiatives.

|                                                                                                                                                                                                                                                                                                                                              | 2011       | 2012 | 2013    | 2014 | 2015 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|------|------|

| Nanoscale Characterization and Defect Detection - Visual and Non-visual <sup>1,2</sup> Atomic and Nanoscale 3D Structure and Defects, including Polymers and other low-Z Materials Nanoscale Probe-Sample Measurement Uncertainty Nanoparticle Monitors for ES&H, which include Size, Dose, and Composition                                  | start      | grow |         |      |      |

| Correlate Nanostructure to Macro-scale<br>Properties <sup>1,2</sup><br>In-Situ, Non-destructive, 3D Imaging of Atomic and Nanoscale<br>Materials<br>In-Situ Measurements that Enable Enhanced Synthetic and<br>Process Control<br>Methods that Resolve and Separate Surface from Bulk<br>Properties<br>Measuring Coupled Nanoscale Phenomena | start      | grow |         |      |      |

| Known Characterization Methods Limits <sup>1,2</sup>                                                                                                                                                                                                                                                                                         |            |      | start   | gro  | w    |

| Metrology for MFD and DFM <sup>2</sup><br>= Integrated Measurement and Modeling Tools<br>= Uniformity Measurements of Nanoscale Properties of Over<br>Large Areas                                                                                                                                                                            | start grow |      | w       |      |      |

| Patterning Metrology <sup>1,2</sup>                                                                                                                                                                                                                                                                                                          |            |      | sustain |      |      |

**Environment, Safety, and Health Research [ESH]:** This thrust explores sustainable, highperformance semiconductor materials and processes for future technologies. During this strategic period, the ESH strategic action plan is to enable new material screening technologies and demonstrate the feasibility of consumable, energy, and water use reduction.

- 2011-2013: Develop new funding approaches and multi-regional initiatives.

- 2011-2015:

- Address strategic high priority ESH research needs, especially with respect to understanding the ESH impact of new and nanomaterials and sustainable processes;

- Increase and maintain visibility of ESH research in other GRC thrusts.

| Near term growth through leverage                                                                                                                                                                                                            | 2011                 | 2012 | 2013    | 2014               | 2015 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|---------|--------------------|------|

| ESH Impact of New and Nanomaterials                                                                                                                                                                                                          |                      |      |         |                    |      |

| New Materials and Associated Processes [Includes<br>packaging materials and processes] <sup>2</sup>                                                                                                                                          | grow<br>grow<br>grow |      |         | sustain<br>sustain |      |

| <ul> <li>ESH for Nanotechnology<sup>2</sup></li> <li>New Technologies for Detection, Hazard<br/>Assessment, and Toxicity Screening <sup>1(20/22),2</sup> [Includes<br/>Dose Definition, Hierarchical Assessment, and Data Mining]</li> </ul> |                      |      | sustain |                    |      |

| ESH/Process Improvement                                                                                                                                                                                                                      |                      |      |         |                    |      |

| Reduction in "Net" Water Use <sup>1(20/22),2</sup>                                                                                                                                                                                           |                      |      | sustain |                    |      |

| Energy: Sources/Utilization/Management <sup>1(20/22),2</sup>                                                                                                                                                                                 |                      |      | start   | gro                | w    |

| Chemical Utilization and Waste Reduction <sup>2</sup>                                                                                                                                                                                        |                      |      | sustain |                    |      |

| Hazardous Chemicals Use Reduction [Includes<br>sustainable chemical substitution] <sup>2</sup>                                                                                                                                               | sustain              |      |         |                    |      |

| Reduction of Hazardous Emissions <sup>2</sup>                                                                                                                                                                                                | sustain decline      |      |         |                    |      |

| Design for ESH/Life-Cycle Analysis <sup>2</sup>                                                                                                                                                                                              |                      |      | start   | gro                | w    |

**Factory System Research [FAC]:** This research area's mission is to provide enabling technology to improve the effectiveness of factory operations.

- 2010: This GRC thrust is scheduled to conclude in December 2010;

- Member companies interested in this research area are exploring alternate funding scenarios, such as an SRC Emerging Initiative.

#### Appendix: NMS Thrust Priorities – Summary of Potential Strategic ETAB/SACC Thrust Changes, i.e. by 2015

#### **Patterning Thrust:**

- Increase: Reduce Variability and Enhance CD, Placement, and Process Control

- Decrease: Nanoimprint Patterning?

#### **Nanoengineered Materials Thrust**

- Increase:

- Materials to Enable 3D Applications\*;

- Process and Material TCAD;

- Decrease: Deterministic Fabrication?\*

#### **Metrology Cross-Thrust:**

- Increase:

- Nanoscale Characterization and Defect Detection Visual and Non-visual

- o Correlate Nanostructure to Macro-Scale Properties

#### **Environment, Safety, and Health Thrust:**

- Increase Through Leverage: ESH Impact of New and Nanomaterials

- Decrease: Hazardous Emissions Reduction?\*

\* These proposed changes require further clarification to ensure strategic NMS SACC-ETAB alignment.

#### **OVERVIEW**

| Science Area: | <b>Device Sciences</b> |

|---------------|------------------------|

| Director:     | Kwok Ng                |

#### MISSION

Device Sciences (DS), through sponsoring university research world-wide, acquires scientific knowledge and innovation in all aspects of semiconductor devices, and meanwhile training highly skilled graduates in pertinent areas, to enable member companies to successful commercialization of differentiated semiconductor-related products.

The areas of interest, aiming at 16-nm generation and beyond, include the Design, Process Technology, Modeling, Characterization, and Reliability of semiconductor devices.

DS is organized into six thrusts:

- Digital CMOS Technologies (DCMOS)

- Non-Classical CMOS Research (NCR)

- Analog and Mixed-Signal Devices (AMS)

- Memory Technologies (NT)

- Device Sciences Modeling and Simulation (DSMS)

- Compact Modeling (CM)

#### **ENVIRONMENT AND TRENDS**

In CMOS scaling, according to the ITRS, it is expected to sustain for the next 15 years. The bulk process will proceed to SOI and eventually the ultimate structure will be 3-D, multi-gate FinFET. Continuing improvement in the areas of high-k gate dielectrics, strain, and source/drain junction and contact will be necessary. At the R/D stage, III-V and Ge semiconductors as alternate channel materials are being studied vigorously. These equivalent scaling techniques are necessary to yield some relief to geometric scaling to keep up with the overall Moore's Law in performance.

In non-volatile memory, the current floating-gate type is becoming harder to maintain the coupling ratio, and the charge-trapping type (SONOS) is foreseen as the dominant structure in the near future. This charge-trapping structure also has the added advantage of 3-D stacking as vertical NAND string to yield the smallest footprint. However, both of these charge-based devices are facing limit in scaling the tunnel oxide, due to the fixed requirement of long retention time. To overcome the limitation, novel non-charge-based device options are being actively pursued. Examples are ReRAM, FeRAM, and MRAM.

In parallel to scaling, one can also gain performance through functional diversification, performance gain without depending on scaling. This can be application-specific chips that involve integration of existing technologies. Examples are embedded flash, mixed-signal technologies and SoC, integrated optics, MEMS, etc. Another area is improvement in reliability and variability. One can certainly improve performance and cost through both. In memory devices, controlling variability will yield multibilit cells. Yet another area is new functional devices–devices that can perform a function which usually requires a circuit block to do. Examples are SRAM and DRAM replacements.

Another industry trend is using multi-core design. In terms of technology requirement, examples are embedded memories, isolation, and 3-D integration. This trend also implies larger systems and more components in a chip. So naturally the issues are reliability and variability, and the requirement of low standby power or low off current. In particular, devices beating the fundamental subthreshold slope of kT/q are interesting options for research.

## **PRIORITIES**

The main overall priorities for DS are listed as follows:

- Track and push ITRS-driven CMOS scaling towards limits.

- Ensure the success of III-V program in NCRC (Non-Classical CMOS Research Center).

- Develop novel non-volatile memories of non-charge-based type.

- Maintain balance of technology and modeling which includes process and device modeling, and compact modeling.

- Ensure synergy, maximize transfer, and avoid overlap between DS and FCRP, in particular MSD and FENA.

Specific priorities per thrust are listed in the following.

#### **Digital CMOS Technologies:**

- Push scaling for the 16-nm node and beyond, to the end of Roadmap. New materials and processes are sought after for this purpose.

- Continue to increase strain to improve mobility.

- Optimize junction and contact to minimize source/drain series resistance.

- Study thin-body MOSFETs not requiring high channel doping (SOI and FinFET).

- Develop low-power technologies with ultra-low off current or/and low supply voltage.

#### NCR:

The goal is to develop MOSFETs of higher performance with alternate channel materials.

- Develop high-k gate dielectrics on III-V or/and Ge with good interfacial properties.

- Optimize source/drain series resistance.

- Study and plan for complementary n-channel and p-channel solution.

- Develop epitaxial growth of III-V or/and Ge materials on Si substrate.

- Research advanced FETs on nano-scale materials of carbon nanotube, graphene, and nanowire.

#### Analog and Mixed-Signal Devices:

- Develop key processes and components for functional diversification (sensors, MEMS...).

- Develop high-performance, low-power I/O devices.

- Optimize active and passive devices for analog and mixed-signal applications.

#### Memory:

- Develop novel non-charge-based non-volatile memory cells (ReRAM, FeRAM, MRAM...).

- Develop 3-D NAND flash with vertical string.

- Explore self-assembly materials and processes.

- Research SRAM and DRAM replacement solutions.

#### Modeling and Simulation:

- Develop advanced modeling tools and techniques for nano-scale materials, processes, and structures for memories.

- Develop advanced process and device modeling tools and techniques for CMOS devices.

#### **Compact Modeling:**

- Develop compact models for beyond-16-nm CMOS devices, including alternate device architectures.

- Develop compact models for analog devices, active and passive.

- Develop compact models for components of functional diversification.

#### **STRATEGIC ACTION PLAN Digital CMOS Technologies**

- There is no core task currently. It is expected to get some core funding for 2011.

- Custom program is substantial in this thrust.

|                                                        | 2011    | 2012    | 2013 | 2014 | 2015 |

|--------------------------------------------------------|---------|---------|------|------|------|

| Advanced structure (FinFET) integration <sup>1,2</sup> |         | sustain |      |      |      |

| High-k dielectrics <sup>1,2</sup>                      | sustain |         |      |      |      |

| Contact and junction technology <sup>1,2</sup>         | grow    | sustain |      |      |      |

| Reliability, variability, metrology <sup>1,2</sup>     | decline | sustain |      |      |      |

1,2 = ETAB,ITRS priority.

#### NCR

- All core funding is put to support NCRC. The 2-year 2nd phase is completing June 2011. SACC will decide on the 3rd phase by ~August 2010.

- Look for leverage funding from outside sources.

|                                                                     | 2011        | 2012 | 2013    | 2014    | 2015  |

|---------------------------------------------------------------------|-------------|------|---------|---------|-------|

| III-V MOSFET, n-channel: Integration <sup>1,2</sup>                 | sustain     |      |         |         |       |

| " : High-k oxide <sup>1,2</sup>                                     | sustain dec |      | decline | sustain |       |

| " : Contact <sup>1,2</sup>                                          | sustain     |      |         |         |       |

| III-V MOSFET, p-channel <sup>1,2</sup>                              | sustain     |      |         |         |       |

| Novel CMOS-like devices (FETs on nanowire, graphene) <sup>1,2</sup> |             |      |         |         | start |

#### Analog and Mixed-Signal Devices

• New cycle starts July 2011. This thrust is expected to grow further. Solicitation process starts September 2010.

|                                                                      | 2011          | 2012 | 2013 | 2014 | 2015 |  |

|----------------------------------------------------------------------|---------------|------|------|------|------|--|

| Noise and isolation <sup>1,2</sup>                                   | sustain       |      |      |      |      |  |

| RF power <sup>1,2</sup>                                              | sustain       |      |      |      |      |  |

| Passives <sup>1,2</sup>                                              | sustain       |      |      |      |      |  |

| I/O devices <sup>1,2</sup>                                           | start sustain |      |      |      |      |  |

| Functional-diversification components (sensors, MEMS) <sup>1,2</sup> | sustain       |      |      |      |      |  |

#### **Memory Technologies**

- New cycle starts August 2011. Solicitation process starts October 2010.

- High proportion of Custom program in this thrust.

|                                                          | 2011    | 2012          | 2013 | 2014 | 2015  |

|----------------------------------------------------------|---------|---------------|------|------|-------|

| Charge-based NVM (FG and CT) <sup>1,2</sup>              | decline | sust          | ain  | end  |       |

| Non-charge based NVM (ReRAM, FeRAM, MRAM) <sup>1,2</sup> | sustain |               |      |      |       |

| 3-D structures <sup>1,2</sup>                            | start   | start sustain |      |      |       |

| Self-assembly processes and devices <sup>1,2</sup>       | st      |               |      |      | start |

| DRAM/SRAM <sup>1,2</sup>                                 | sustain |               |      |      |       |

#### **Modeling and Simulation**

- Funding roughly equal for device and process modeling.

- New cycle starts January 2012. Solicitation process starts March 2011.

|                                                        | 2011    | 2012 | 2013 | 2014 | 2015 |

|--------------------------------------------------------|---------|------|------|------|------|

| Process simulations for CMOS & Memories <sup>1,2</sup> | sustain |      |      |      |      |

| Device simulations for CMOS <sup>1,2</sup>             | sustain |      |      |      |      |

#### **Compact Modeling**

• New research cycle starts January 2013. No solicitation in near future.

|                                                   | 2011    | 2012    | 2013 | 2014 | 2015 |

|---------------------------------------------------|---------|---------|------|------|------|

| Advanced CMOS (FinFET, multi-gate) <sup>1,2</sup> |         | sustain |      |      |      |

| Analog & mixed-signal devices <sup>1,2</sup>      | sustain |         |      |      |      |

| Reliability & variability <sup>1,2</sup>                        | sustain |       |  |  |

|-----------------------------------------------------------------|---------|-------|--|--|

| Novel CMOS structures (III-V, nanowire) <sup>1,2</sup>          |         | start |  |  |

| Functional-diversification components (sensor, energy) $^{1,2}$ | sustain | grow  |  |  |

## **OVERVIEW**

| Science Area: | Interconnect and Packaging Sciences |

|---------------|-------------------------------------|

| Director:     | Scott List                          |

#### MISSION

The IPS has three components of its mission:

- To create and explore advanced evolutionary, revolutionary, and transformative technologies for connecting elemental devices (transistors, capacitors, nanodevices, etc.) to each other and to the macro world targeting the 16nm node and beyond, including 3D and heterogeneous integration;

- To facilitate strong bridges and foster new ideas between the packaging and interconnnect communities and develop closer ties to the system and design communities in universities; and

- To educate talented professional staff in the areas of Interconnect and Packaging Science through sponsored, innovative university research.

#### **ENVIRONMENT AND TRENDS**

In general the progress on Cu/low k replacements such as CNTs, graphene, optical interconnect has not been sufficient to warrant the integration of these options into the IPS portfolio. Over the past few years, research on CNTs and other "alternate interconnects" have shown that it will be harder to replace Cu-low k than anticipated at first glance. CNTs have severe limitations concerning controlled growth, high density, chirality control, contact resistance and kinetic inductance. Optical interconnects currently use too much power and area for nearly all on die interconnects and molecular interconnects are too slow. In addition, any new choice for local interconnect must be chosen to interface well with any new technology chosen for the next switch. These Cu/low k replacement options will continue to be generally delegated to the IFC for research.

There has also been an increasing trend to both increased functionality and functional diversification. This diversification has manifested itself differently in the various member companies. Specific emerging applications include sensors, energy harvesting, bio-compatible electronics, extreme miniaturization, multi-cores and memory. These applications drive a new need for 3D packaging, 3D interconnect, MEMs, board level interconnect, a better interface with design and system, bio-compatible packaging, extreme bandwidth to memory solutions and new, interconnect centric memory research.

The continued push for integrating new materials into smaller dimensions has generated an increased need for improved metrology and modeling for both the BEP and PKG thrusts. With current metrologies, structures and interfaces are no longer clearly resolved and there is an increasing need to image in three dimensions with atomic resolution for buried interfaces. As structures become smaller and more complex, current models are both more difficult to converge and validate.

In addition to the technological trends described above, there have been two major environmental factors affecting the IPS area which have had a substantial impact on the formulation and execution of the 2010 strategic plan. These factors are the potential instability in sources of matching state funding and a shift in funding from the BEP to the PKG thrust.

Given the very difficult budgetary constraints of many state governments during the economic downturn of the last two years, commitments of continued state funding are increasingly difficult to secure. In

particular, we experienced a substantial reduction in our state matching funding commitments for 2010 which had potentially profound impacts on our portfolio. In response to these reductions, we explored both contract to grant conversions as well as the identification of additional sources of matching funding to offset such reductions. For 2010, we were fortunately able to secure new sources of matching funding to supplement specific losses with the creation of another research center. In particular, the Center for Electronic Material Processing and Integration (CEPMI) was formed in 2010 at the University of North Texas. Its current focus includes both low k materials and plasma processing. In the future, its focus may expand to include both 3D and packaging initiatives if additional state or corporate funding becomes available. In the future, we need to proactively explore new sources of matching funding to our researchers.

Due to the decrease in emphasis of fab related processing of several of our members, there has been a continuous shift in the relative priority between funding for BEP and PKG tasks. This has resulted in a substantial, approximately 20%, relative reduction in the BEP budget and a proportionate increase in the PKG budget over the last two years. Coupled with an overall budget cut to the science area, the BEP thrust has had to significantly streamline their research portfolio to focus on core Cu / low k extendibility issues.

## **PRIORITIES**

The current strategy for IPS is to continue to emphasize specific features of the BEP and Packaging thrust portfolios while at the same time addressing the inter-thrust issues through the clearly defined interface area. The IPS is targeting the 16 nm node and beyond. BEP emphasis continues to be ensuring the viability and reliability of Cu / low k interconnects. There are increased interactions with design to better define the needs and potential for different interconnect solutions. There is also an increased emphasis on predictive modeling, nanometrology capabilities and interconnect centric memory research. Packaging research continues to push thermal management and control, I/O, power delivery and fundamentals of lead-free solder. There is also a growing need to explore interactions between biological systems and electronic packages among other applications to accommodate the functional diversifications needs of the industry. The interface area focuses on 3D, die/package mechanical interactions, passive integration, thermal management and functional diversification. In general the IPS research priorities span the twelve ETAB priorities described below, listed in descending order of collective prioritization:

- Development of novel 3D IC processes and architectures

- Thermal, mechanical and electrical metrology / modeling for nanoscale materials and structures

- Reliable interconnects to 16nm and beyond

- Manufacturing options for reducing variability and enhancing reliability

- New materials and processes for interconnects and packaging

- Novel interconnect structures (including optical)

- Ideas to increase bandwidth and I/O

- Novel approaches for heat removal including novel packaging materials and advanced thermoelectric cooling structures

- Integration of passives and sensors in die or on package

- Compact modeling for interconnect system modeling, package modeling, chip-package power modeling and design

- Emerging materials and passives for analog and mixed signal applications

• ESH: Processes for interconnect technologies, consumables use and disposal, new material screening

## STRATEGIC ACTION PLAN

IPS

- Identify additional and more stable sources of matching funding for both BEP and PKG research

- Expand 3D and heterogeneous system in a package integration research within IPC

- Increase interaction with design to better define the needs and potential for different interconnect and thermal solutions

- Continue pursuing interface research on a voluntary basis within each thrust

- Pursue co-funding tasks with ICSS for interconnect/design optimizations

- Drive 3D research through both the IPC and CAIST centers

- Explore interactions between biological systems and electronic packages

- Interact with IFC technical programs and management through workshops and reviews to insure portfolio rationalization

- Continue joint funding with NSF of multi-core tasks

- Expand reliability and metrology initiative with NIST